#### **RESEARCH ARTICLE**

• OPEN ACCESS Received: 15-05-2022 Accepted: 15-07-2022 Published: 27-08-2022

**Citation:** Sehgal J, Kumar M (2022) 12-Bit Clock Gated SAR-ADC for Bio-Medical Applications. Indian Journal of Science and Technology 15(34): 1648-1654. https://doi.org/ 10.17485/IJST/v15i34.1033

<sup>°</sup> Corresponding author.

jyotiece.rs.uiet@mdurohtak.ac.in

#### Funding: None

#### Competing Interests: None

**Copyright:** © 2022 Sehgal & Kumar. This is an open access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

#### ISSN

Print: 0974-6846 Electronic: 0974-5645

# 12-Bit Clock Gated SAR-ADC for Bio-Medical Applications

#### Jyoti Sehgal<sup>1</sup>\*, Manoj Kumar<sup>2</sup>

1 Research Scholar, UIET, MDU, Rohtak, Haryana, India 2 Assistant Professor, UIET, MDU, Rohtak, Haryana, India

# Abstract

Background/Objectives: Power optimization is a critical design criterion in modern integrated circuits. The unwanted clock signals are neutralized and the reduction in power consumption is made presumable by using the clock gating technique. Methods: Analog-to-digital converters (ADCs) are important components in these systems. A widely used successive approximation register A/D converter includes an internal clock, reference, and high resolution. The number of redundant cycles is increased with improved resolutions but enhances the consumption of power. Thus, the clock gating strategy is used to substantially lower the circuit's dynamic power consumption. The clock gating technique is implemented with a reduced number of transistors to minimize the overhead with high switching activity. Also, demonstrate no imperfection on the clock duty cycle. Findings: A 12-bit clock gated SAR register using a D-flip flop with 1.8 V supply voltage is proposed in this study for efficient biomedical applications. SAR without a clock gating technique consumes 54  $\mu$ W of power and SAR with a clock gating technique consumes a power of 22.68  $\mu$ W. **Novelty:** The clock gating technique is stipulated to minimize power consumption of clock gated SAR-ADC and improves the battery life of the portable device.

**Keywords:** Clock gated technique; power consumption; resolution; SARADC; successive approximation register

## 1 Introduction

Because of the upsurge in chip complexity, reduced power and small size are major contradictions in modern integrated circuits. Multitudinous proposed techniques capitulate low-power operation with minimized signal switching activity. The clock system is one of most power swallowing submodules in VLSI circuits, thus the proposed clock gating technique is a useful approach to different hierarchical levels to reduce power consumption as well as diminish the number of transistors with reduced switching activity. An A/D converter plays a vital role in transferring analog signals to digital codes in Bio-Medical applications, VLSI systems, and wireless systems<sup>(1,2)</sup>. In comparison with other ADCs, successive approximation register (SAR) ADC is mostly used ADC in Bio-Medical applications like Bio-Medical sensors, medical imaging, data acquisition systems, and implanted biomedical devices like a pacemaker<sup>(3)</sup>.

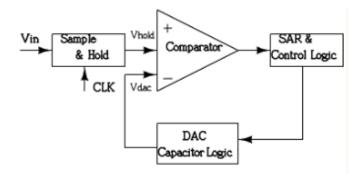

Low-frequency analog signal conversion demands ultra-low-power operation (e.g., in nW range). The binary search algorithm<sup>(4)</sup> is the basic principle on which successive approximation register ADC mainly works. Following [Figure 1] presents a process design model of SAR-ADC.

The four major blocks in [Figure 1] are the Sample and Hold circuit, comparator, DAC (Digital to Analog converter) capacitor logic, and SAR Control Logic. The conversion is completed in numerous clock cycles by SAR ADC, which uses the information from the last determined bit. Analog values are stored in the sample hold circuit. It gives a constant voltage to the comparator during conversion. The basic purpose of the comparator is to compare both the outputs from digital to analog converter  $V_{dac}$  and from the sample and hold circuit  $V_{hold}$ , and generates the output in the digital form of either '0' or '1' which is provided to SAR Logic. The binary search algorithm is implemented by the SAR logic. SAR logic gives the output in binary format which is further converted to the corresponding analog value using DAC and given to the comparator. All the devices utilized in SAR ADC consume a lot of power. Thus various techniques like clocking system, reducing the leakage, and logic reordering are used to resolve the challenge regarding consumption of the power. In this paper, a 12-bit clock gated SAR analog to digital converter is designed on 180nm CMOS technology at a 1.8V supply.

Fig 1. Model of Successive Approximation Register ADC

Erkan Alpman et al.<sup>(4)</sup> present a C-2C SAR ADC that culminates in high performance by using a small-area architecture and conquering a high device threshold. Shuo-Wei Michael Chen et al.<sup>(5)</sup> provide a high-speed (600-MS/s) and medium-resolution (6-bit) conversion using improved ADC. Zhiheng Cao et al.<sup>(6)</sup> present an ADC that achieves 6b performance without any digital post-processing. Mohamed O. Shanker et al.  $^{(7)}$  proposed a clock gating SAR ADC. It can reduce the redundant clock by activating the clock gated signal (Clkg) with a change in the state of the flip flop. This will cause a decrease in the dissipation of power. Magdy A. Bayoumi et al.<sup>(8)</sup> the clock signal is implemented using a register with no data switching activity. It operates with fewer transistors and no redundant transitions which makes it suitable for low-power applications. Mohamed O. Shaker, and Magdy A. Bayoumi<sup>(9)</sup> proposed a novel low-power clock gated flip flop to reduce the gating overhead. T.O. Anderson et al.<sup>(10)</sup> have discussed two basic types of logic one for the sequencer and the other for the code register as two separately distinguished items. Auxillary control logic is also used for speeding up the conversion cycle. A. Rossi et al.<sup>(11)</sup> proposed a non-redundant SAR ADC with a multiple-input n-bit shift register. It is essential to provide a mechanism that brings the shift register into the initialization state. One method of loading the initialization is to use flip-flop with reset and set lines connected to a control signal which if active, sets the MSB flip-flop and resets all other bits. To stop the conversion we can use OR chain applying to the LSB a control signal which if active forces '1' in all signals. So SAR operates in the memorization mode. The stop signal is useful in a particular when the last step of the approximation sequence is reached and the result of the conversion process gets stored. The output of the LSB flip-flop can be used to signal the end of the conversion. The proposed non-redundant SAR ADC saved up to 50% of the total area. Strollo et al.<sup>(12)</sup> proposed two clock gating techniques. Double Gating is the first technique that is performed individually on the master and slave latches. As the switching activity of the input signal is very low, the power dissipation gets reduced. A second technique is  $NC^2MOS$  Gating or Sequential Gating, in which the entire flipflop requires only one gate logic. The NC<sup>2</sup>MOS gated flip-flop saves 74 percent of the power when the input is idle, however, the double-gated flip-flop retains 64 percent. Due to its lower complexity, the NC<sup>2</sup> MOS gated flip-flop performs better than the double-gated flip-flop<sup>(13)</sup>. The clock gating flip-flop in a 16-bit counter saves up to 52% of the power while the 8-bit audio sampler NC2MOS gated flip-flop saves 16% of the power. Manoj et al. <sup>(14)</sup> have designed the SAR register in 180nm technology using the clock gating technique. By using clock gating, power was reduced from  $54\mu$ W to 736.1nW. Due to the existence of redundant clocks in a conventional SAR, during the entire conversion process, every flip-flop changes its state once or twice. Such difficulty can be solved by the means of the clock gated flip-flop. The transition in clk states depends on frequency. Nandita

(1)

Srinivasa et al.<sup>(15)</sup> have used the Spartan 3 FPGA family, power has been calculated using the clock gated benchmark circuits. Despite an area trade-off, it has been observed that the power shrinks. Wing-Kong Ng et al.<sup>(16)</sup> proposed flip-flop technology with two dynamic latches in parallel connection improve the race tolerace, energy efficiency, and circuit compactness.

## 2 Methodology

## 2.1 Conventional SAR

The conventional Successive approximation Register<sup>(11)</sup> contains many N-bit ring counters and also multiplexer is connected with the kth FF to choose one data input coming from:

- 1) Right shift [( k+1)th FF output]

- 2) Load data (comparator output)

- 3) Memorization (kth FF output itself)

The operation of the 12-bit successive approximation register is given as: Initially, SAR assumed all the bits are '0' except MSB. MSB is assumed '1'. At the first clock cycle, the comparator allocated MSB a true value (x11), and the second MSB becomes '1'. Until then all the true values are allocated to MSB, and this procedure will continue. Equation (1) is realized to stop the conversion procedure by adding OR logic gate chain:

a0 = Stop

a(k) = a(k-1) + Q(k-1)

Equation (1) is used at the last conversion of the last step and its result is stored in SAR. Here we notice that every FF requires 'n' clocks to finish the conversion process which indicates that we require  $n^2$  clocks for the whole conversion process. During the whole conversion process, the state of every FF varies once or twice and because of this, a large no. of redundant clock pulses occurs which dissipates power without affecting the FF<sup>(8)</sup>.

#### 2.1.1 Various Clock Gating Techniques

2.1.1.1 AND gate logic-based Clock gating . A gating clock is a common way to minimize power consumption. Because of the simplicity AND gate is mostly used gate logic is for the clock gating technique<sup>(14)</sup>. When the enable signal is high 4 bit counter increases its value by 1 count. Mostly the AND logic gate is utilized for negative edge triggering because, in positive edge triggering, glitches occur because of the larger falling time.

2.1.1.2 NOR gate Logic-based Clock gating . NOR gate is another important logic gated that is used for the gating clock technique. For clock gating purposes, we consider 2 inputs NOR logic gate. The O/P of the NOR gate is '1' When both the inputs are '1' only then the output is '1', otherwise, it will be '0'. A NOR logic gate<sup>(17)</sup> is utilized for positive triggered circuits.

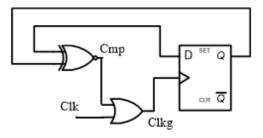

2.1.1.3 D-type flip flop-based Clock gating. [Figure 2] shows the D flip-flop clock gating for the negative latch<sup>(18)</sup>. In this architecture, we use the XNOR logic gate and OR logic gate. Inputs of the XNOR gate are provided by the input D and output Q. The output of the XNOR logic gate is given to one of the inputs of the OR logic gate. The transition occurs due to different input and output logic. This design provides a low switching feature.

Fig 2. D-flip flop clock gating

### 2.2 Proposed Clock gated SAR methodology

The binary search algorithm is implemented by the SAR logic. Two different proposals are presented to design SAR control Logic. The first proposal is given by Anderson<sup>(11)</sup> in which a successive approximation Register consists of a shift register. This proposal is employed by '2N' flip-flops. The next proposal which comprises some combinational logic and 'N' no of flip-flops are presented by A. Rossi<sup>(11)</sup>. SAR Control logic works sequentially and produces output based on the resulting output of the comparator. Initially, MSB is set to '1' and DAC converts this digital value to the analog value and then the comparator compares this value with the sampled value<sup>(19)</sup>. Then it is the comparator's choice whether MSB remains the same or it changes to '0'. The same conversion process is repeated throughout the whole process. Here we notice that two clocks are active during each conversion.

#### 2.2.1 The Transmission Gate Based D Flip Flop

D flip-flop is the fundamental unit of the Successive approximation register. For low power requirements, a D flip flop-based transmission gate is used<sup>(20)</sup>. To boost power efficiency, minimum size transistors are more efficient<sup>(21)</sup>. In the critical path, transistors whose threshold voltage is low are used and in the noncritical path, transistors whose threshold voltage is high are used to decrease the leakage power. High efficiency is thus given by this dual-threshold strategy.

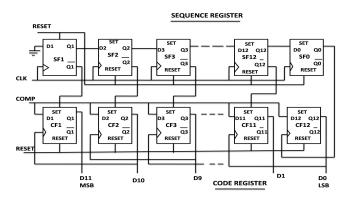

#### 2.2.2 Sequence and Code Register architecture

Successive approximation Register block diagram is shown in [Figure 3]. Two sets of registers used in this architecture are sequence registers or Sequencer and Code registers<sup>(22)</sup>.

Fig 3. Block Diagram Successive Approximation Register

The sequence register is used for bit sequencing, while the code register retains bit values<sup>(23)</sup>. The Q bar output of the shift register is used to set the FFs of the code registers. Initially, the reset of the first FF of the sequence register is attached to the reset of the remaining FFs of the sequencer, and the set input of the 1st FF and reset of all the FFs of the code register<sup>(24)</sup>. Firstly, 0V supply voltage is provided to the reset input. O/Ps of the non-inverted and inverted are '0' and '1' respectively. The non-inverted output also determines the set input of CF1 and its output becomes 1<sup>(25)</sup>. The MSB is stored in it and the weight for the full-scale range is 0.5Vref. Here we note that all sequence registers are reset, and all code registers except CF1 are set. Now, DAC generates its equivalent analog value. When the 1st clock pulse is triggered, reset goes high and output Q of the 1st FF becomes '0' as D input to the first flip is grounded and the output of SF2 is '1'<sup>(15)</sup>. Thus, the transition occurs from low to high. SF2 triggers CF1 and stores comparator output. When another clock pulse is applied, the FF of the code register retains the set value as SF2 output becomes '0'. This process is repeated for each flip-flop until the sequence register's FF outputs high logic after N clock cycles.

The traditional SAR possesses several redundant clock pulses. This happens because the state of every FF varies once or twice throughout the whole conversion process. The redundant clock pulses are reduced by the use of Clock gated FF.

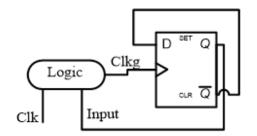

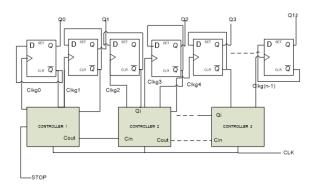

The FF input gets the logic output and leaves the CLK signal isolated. In a particular period, the condition of the CLK signal is changed based on its frequency. As a result, many extra pulses occur that consume power. By using Clock gating FF, this issue can be solved as shown in [Figure 4]. The output Q is connected to the input D. By doing this, the Clkg signal is active if the FF decides to vary its state. The Clkg signal is inactive if the FF retains its condition. The n-FF Clock gated Successive

approximation register has (n+1)/3 controllers. [Figure 5] shows the proposed clock gated SAR register block diagram. Clkg signal is generated by the controllers to control a set of FFs. Each FF output is linked with the corresponding controller. Each FF output is connected for toggling operation to the FF input terminal. Each FF at the positive edge of its Clkg is triggered. Controller 1 and controller 2 are mostly similar to each other. Only one difference is that the transistor M10 is driven by Cin, whereas in controller 1 the transistor M8 is driven by Clk. In the controller, an additional transistor M9 is used which is driven by Qi.

Every controller has a gating overhead circuit. The gating overhead circuits contain pass transistors which are used for the propagation of the clock signal. The MSB loads the true value of the data, modifying its state. They often change their state as other bits load their real value or collect the data coming from the neighboring FF (shift right).

Fig 4. Clock Gated Flip Flop

Fig 5. Proposed clock gated SAR Register block diagram

# 3 Result and Discussion

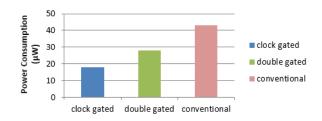

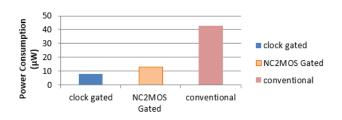

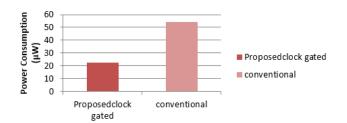

The performance of clock gated SAR are compared with double gated and NC<sup>2</sup>MOS gated SAR. The simulated result of the SAR Logic is deployed at 180 nm CMOS technology at 1.8V supply at 0.5 KS/s. As compared to conventional SAR, the proposed clock gated SAR saves 58% and by comparing to the double gated SAR, it saves 35.7% of the power as shown in [Figure 6]. As compared to conventional SAR, the proposed clock gated SAR saves 81.4% and by comparing it to the NC<sup>2</sup>MOS gated SAR, it saves 38.4% of the power as shown in [Figure 7]. [Figure 8] shows the power consumption of proposed clock gated SAR and conventional without clock gating. The power consumption without clock gating is  $54\mu$ W and with clock, gating is  $22.68\mu$ W. As in the proposed SAR register, no transistor count is raised, but total power consumption is decreased by 58 percent. [Table 1] shows the comparison of conventional SAR, other reported SAR, and proposed clock gated SAR based on the various parameters like the technology used, supply voltage, resolution, number of transistors required, and consumption of power. From Table 1, the consumption of the power in SAR Register without clock gating technique. But the number of transistors is increased in the clock gated SAR.

| I                  |        |                                   |                          |

|--------------------|--------|-----------------------------------|--------------------------|

| Parameters         | (17)   | Conventional SAR with clock gated | Proposed clock gated SAR |

| Technology (nm)    | 180    | 180                               | 180                      |

| Resolution (bits)  | 8      | 12                                | 12                       |

| Supply Voltage (V) | 1.8    | 1.8                               | 1.8                      |

| Sampling Rate      | 35MS/s | 0.5KS/s                           | 0.5KS/s                  |

| Power consumption  | 65µW   | 54µW                              | 22.68µw                  |

Fig 6. Analysis of power consumption with double gated SAR

Fig 7. Analysis of power consumption with NC2MOS gated SAR

Fig 8. Power consumption of proposed clock gated and conventional SAR

# 4 Conclusion

A 12-bit SAR has been implemented to minimize the repeated cycles of the clock signal for Bio-Medical applications. The proposed  $NC^2MOS$  gated SAR saves more power percentage as compared to double-gated SAR. The proposed system does not demand any constraint on the clock duty cycle. In 180nm CMOS technology, the SAR with a clock gated system with double gated SAR and  $NC^2MOS$  gated SAR have been introduced using a 1.8V power supply. In the future, this technique will be used to design a biopotential system with improved battery life.

## References

- Limotyraskis S, Kulchychi SD, Su D, Wooley BA. A 150MS/s 8b 71mW time-interleaved ADC in 0.180µm CMOS. In: and others, editor. Proc. IEEE Int. Solid-State Circuits Conference Dig. Tech papers. 2004;p. 258–259.

- Soliman A, Mahmoud, Salem HA, Albalooshi HM. "An 8-bit, 10KS/s, 1.87µW Successive approximation analog to digital converter in 0.25µm CMOS technology for ECG detection systems. Proceeding of the circuits, systems, and Signal Processing. 2015;34. Available from: https://doi.org/10.1007/s00034-015-9973-z.

- 3) Martin J, Kramer E, Janssen K, Doris B, Murmann. A 14 b 35 MS/s SAR ADC Achieving 75 dB SNDR and 99 dB SFDR With Loop-Embedded Input Buffer in 40 nm CMOS. *IEEE Journal of Solid-State Circuits*. 2015;50(12):2891–2900. Available from: https://doi.org/10.1109/JSSC.2015.2463110.

- 4) Alpman E, Lakdawala LRH, Carley K, Soumyanath. A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP digital CMOS. In: 2009 IEEE International Solid-State Circuits Conference - Digest of Technical Papers;vol. 77. 2009;p. 76–77. doi:https://doi.org/10.1109/ISSCC.2009.4977315.

- 5) Chen SWM, Brodersen RW. A 6-bit 600-MS/s 5.3-mW Asynchronous ADC in 0.13-CMOS. *IEEE Journal of Solid-State Circuits*. 2006;41(12):2669–2680. Available from: https://doi.org/10.1109/JSSC.2006.884231.

- 6) Cao Z, Yan S, Li Y. A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13-CMOS. *IEEE Journal of Solid-State Circuits*. 2009;44(3):862-873. Available from: https://doi.org/10.1109/JSSC.2008.2012329.

- Shaker MO, Bayoumi MA. A clock gated flip-flop for low power applications in 90 nm CMOS. 2011 IEEE International Symposium of Circuits and Systems (ISCAS). 2011;p. 558–562. Available from: 10.1109/ISCAS.2011.5937626.

- Shaker MO, Bayoumi MA. A clock gated Successive approximation register for A/D conversions. *Journal of circuits, systems, and computers*. 2014. Available from: https://doi.org/10.1142/S0218126614500236.

- 9) Shaker MO, Bayoumi M. Novel clock gating techniques for low power flip-flops and its applications. 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS). 2013;p. 420–424. Available from: https://doi.org/10.1109/MWSCAS.2013.6674675.

- 10) Anderson TO. Optimum control logic for Successive Approximation Analog to Digital converters. Computer Design. 1972;11:81–86.

- 11) Rossi A, Fucili G. Nonredundant successive approximation register for A/D converters. *Electronics Letters*. 1996;32(12):1055–1055.

- 12) Strollo AGM, Napoli E, De Caro D. New clock-gating techniques for low-power flip-flops. *Proceedings of the 2000 international symposium on Low power electronics and design ISLPED '00.* 2000;p. 114–119. Available from: https://doi.org/10.1145/344166.344540.

- 13) Strollo AGM, Napoli E, De Caro D. Low-power flip-flops with reliable clock gating. *Microelectronics Journal*. 2001;32(1):21-28. Available from: https://doi.org/10.1016/S0026-2692(00)00072-0.

- 14) Kumar M, Kumar R. A Ultra Low Power 12 Bit Successive Approximation Register for Bio-Medical Applications. International Journal of Engineering & Technology. 2018;7(3.16):98–98.

- Srinivasan N, Prakash NS, Shalakha D, Sivaranjani D, Lakshmi GSS, B. Bala Tripura Sundari, Power Reduction by Clock Gating Technique. 2015;21:631– 635.

- Wing-Kong, Ng WS, Kok CWT. Double Edge-Triggered Half-Static Clock-Gating D-Type Flip-Flop. Solid State Electronics Letters. 2021;3:1–4. Available from: https://doi.org/10.1016/j.ssel.2021.08.001.

- 17) Chindhu ST, Shanmugasundaram N. Clock Gating Techniques: An Overview. 2018 Conference on Emerging Devices and Smart Systems (ICEDSS). 2018;p. 217–221.

- 18) Tasnim B, Nazzal MS. A 1V 8bit 0.84µW SAR ADC for Bio-Medical applications. 13th International SoC Design Conference (ISOCC). 2016.

- 19) Guo W, Liu S, Zhu Z. An asynchronous 12-bit 50MS/s rail-to-rail Pipeline-SAR ADC in 0.18µm CMOS. Microelectronics Journal. 2016;52:23–30.

- 20) Ma R, Wang L, Li D, Ding R, Zhu Z. A 10 bit 100MS/s 5.23mW SAR ADC in 0.18um CMOS. "Microelectronics Journal. 2018;(78):63-72.

- 21) Zhou X, Zhang Y, Su Y. An 8-bit 35-MS/s successive approximation register ADC. 2015 IEEE International Conference on Progress in Informatics and Computing (PIC). 2015;p. 531–533. Available from: https://doi.org/10.1109/PIC.2015.7489904.

- 22) Xin X, Cai JP, Chen TT, Yang QD. A 0.4-V 10-bit 10-KS/s SAR ADC in 0.18 μm CMOS for low energy wireless senor network chip. *Microelectronics Journal*. 2019;83:104–116. Available from: https://doi.org/10.1016/j.mejo.2018.11.017.

- 23) Nasiri H, Abdolrezanabavi. A 1.8V 3GS/s 7-bit time-interleaved Quasi C-2C SAR ADC using Voltage comparator time information. AEU-International journal of electronics and communication. 2017. Available from: https://doi.org/10.1016/j.aeue.2017.08.28.

- 24) Gary K, Yeap. Practical Low-Power Digital VLSI Design. Kluwer Publishing. 1998.

- 25) Wakerly JF. Digital Design Principles and Practices. Prentice-Hall. 2005.