#### **RESEARCH ARTICLE**

• OPEN ACCESS Received: 06.10.2020 Accepted: 23.09.2021 Published: 11.10.2021

**Citation:** Esmaeili SE, Imdoukh A (2021) Decreasing the Power-Clock Resonant Signal Central Voltage as a Mean for Power Reduction in Integrated Power and Clock Distribution Networks. Indian Journal of Science and Technology 14(33): 2671-2683. https://doi.org/ 10.17485/IJST/v14i33.1820

#### <sup>©</sup> Corresponding author.

sesmaeili@auk.edu.kw

**Funding:** This research work was funded by the American University of Kuwait

#### Competing Interests: None

**Copyright:** © 2021 Esmaeili & Imdoukh. This is an open access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

Published By Indian Society for Education and Environment (iSee)

#### ISSN

Print: 0974-6846 Electronic: 0974-5645

# Decreasing the Power-Clock Resonant Signal Central Voltage as a Mean for Power Reduction in Integrated Power and Clock Distribution Networks

#### Seyed E Esmaeili<sup>1\*</sup>, Abeer Imdoukh<sup>2</sup>

**1** Assistant Professor, Engineering Department, American University of Kuwait, Safat, 13034, Salmiya, Kuwait

**2** Instructional Assistant, Engineering Department, American University of Kuwait, Safat, 13034, Salmiya, Kuwait

# Abstract

Background/Objectives: Density, performance, and design complexity of integrated circuits are rapidly increasing specifically in 3-D integration where multi-plane synchronization is required. The power and clock distribution networks consume a large portion of the limited on-chip metal resources. In order to reduce the metal overhead associated with the power, global clock, and local clock distribution networks, the concept of an integrated power and clock distribution network (IPCDN) was investigated and correct functionality of combinational and sequential elements verified. This study discusses potential power savings in IPCDNs achieved by reducing the central voltage at which the signal oscillates. Methods/Statistical analysis: In this paper, an IPCDN with differential power-clock signals centered at half the supply voltage is proposed to further reduce the power consumption. The elements of the proposed scheme including the LC differential power-clock driver, clamping circuit, clock buffer, and voltage doubler have been simulated using Tanner 0.25 um CMOS technology at a frequency of 50 MHz and a supply voltage of 2.5 V. Findings: Simulation results indicate that the proposed scheme achieves 75.32% and 76.47% power reduction in the LC differential powerclock driver and clock buffer, respectively. The effects of process, voltage supply, and temperature (PVT) variations on the proposed scheme were also investigated. **Discussion:** The IPCDN has a large capacitance and is heavily loaded, thus reducing the central voltage of the resonant sinusoidal signal flowing in this network enables significant reduction in power consumption. Novelty/Applications: The proposed scheme enables power reductions in the LC differential power clock driver and clock buffer. The effects of process, voltage supply, and temperature (PVT) variations on all circuit elements of the proposed scheme was investigated.

**Keywords:** resonant clocking; power reduction; routing complexity; LC clock driver; clock buffer; clamping circuit; voltage doubler

#### **1** Introduction

The clock distribution network (CDN) distributes the clock signal which acts as a timing reference that controls and synchronizes the flow of data. The CDN operates at high frequencies, is heavily loaded, and has a high capacitance. The CDN in synchronous systems-on-chip (SOCs) and application-specific-integrated-circuits (ASICs) consumes a large amount of power compared to the whole system<sup>(1,2)</sup>. In high performance processors, more than 30% of total power is consumed in the CDN<sup>(3-7)</sup>. In the IBM POWER4 1.3 GHz microprocessor, around 70% of total power is dissipated in the CDN and latches<sup>(8)</sup>. Latest developments in 3-D integrated circuits where multi-plane synchronization is required, indicate that the power consumption and metal overhead associated with the CDN will remain at these high levels<sup>(9,10)</sup>.

Energy recovery resonant clocking is an appealing scheme to reduce the power consumption of the CDN. The resonant clocking scheme, unlike square-wave clocking, uses the capacitance of the clock network, an on-chip inductor, and a decoupling capacitance to generate a resonant sinusoidal clock. Resonant CDNs reduces power by recycling and transforming the energy between electrical and magnetic form in the capacitor and inductor, respectively. The LC resonant clock driver implemented on a 22 nm process node achieves 50% power reduction in the driver as compared to the non-resonant driver<sup>(11)</sup>. The modified Cell Broadband Engine Processor incorporating a large resonant global clock network demonstrates a 6-8 Watt power savings<sup>(12)</sup>. Measurement results using intermittent resonant clocking (IRC) show that resonant clocking reduces the clock power by 36% at 980 kHz compared to conventional non-resonant clocking<sup>(13)</sup>. Simulation results of 1024 clocked flip-flops through an H-tree clock network driven by a resonant clock generator indicate total power savings of up to 83% and a power reduction of 90% on the clock-tree as compared to the same implementation using conventional square-wave clocking<sup>(14)</sup>. The distributed model of a two-level resonant H-tree structure presented in (15) exhibits 84% decrease in power dissipation as compared to a standard H-tree clock distribution network. AMD's x86-64 resonant clock design for a power-efficient high-volume microprocessor achieved a peak 25% power reduction in the global clock  $^{(16)}$ . Varying the operating frequency, LC tank placement, and sizes in a 3-level resonant clock H-tree demonstrates that around 23% power reduction is achieved when the LC tank is placed on the second level of the clock network<sup>(17)</sup>. Implementing compensation capacitors to reduce the overhead of the on-chip inductor and capacitor resources, resulted in a 12% reduction in passive device area while still achieving 49.9% power savings as compared to traditional square-wave clock<sup>(18)</sup>. In<sup>(19)</sup>, a modeling and optimization method for resonant clocking using the mesh clock structure was proposed since the mesh clock structure has a higher power consumption as compared to H-tree. The experiment demonstrated that the resonant clock mesh structure can save more than 80% of power consumption compared to the same mesh structure without using the resonant LC tanks. A successful experiment on a test-chip in 130-nm CMOS technology at 1.56 GHz LC resonant clock directly driving 2x896 flip-flops illustrates that resonant clocking results in 57% lower clock power and 15-30% lower total chip power as compared to conventional clocking $^{(20)}$ .

Various schemes have been proposed in the literature to enable further power reduction in the resonant clock distribution network. Dual-edge triggered flip-flops operating with a resonant sinusoidal clock signal can achieve up to 58% reduction in power consumption<sup>(21)</sup>. Clock gating has been used to reduce the resonant clock power consumption<sup>(22,23)</sup>. However, the global clock distribution network driving the clock gates still consumes a large amount of total power<sup>(24,25)</sup>. A resonant converter with voltage doubler rectifier for wide output voltage with soft switching characteristics is presented in<sup>(26)</sup>. A full-bridge rectifier and voltage-doubler are employed for low-voltage and high-voltage output applications. Quasi-resonant clocking with voltage-frequency scalable resonant clocking system was proposed in<sup>(27)</sup>. The proposed scheme uses a timing control module to control the assertion/de-assertion of the signals generated to ensure efficient operation. A two-phase synthesis algorithm for resonant clock networks supporting dynamic voltage/frequency scaling is discussed in<sup>(28)</sup>. The first phase in the algorithm is the allocation and placement of the inductor and the second phase is the resizing of the driving buffers. Simulation results show that resonant clock networks synthesized using the proposed algorithm achieve 17% reduction in power. In<sup>(29)</sup>, a quadrature resonant clock generator with tuning capacitors and amplitude control feedback loop is presented. The proposed clock generator enables 20 to 25% reduction in power as compared to conventional CMOS clock driver. A resonant clock driver for low-power and low-voltage for IoT device was simulated in<sup>(30)</sup>. The proposed clock driver operates under a low supply voltage and a voltage doubler to reduce the on-resistance of the NMOS transistor.

Integrated circuits (ICs) density, performance, and design complexity are increasing specifically in 3-D integration (31-33), which emphasizes the need for new techniques to supply the power, ground, and clock signals. A large portion of the limited onchip metal resources are consumed by the power and clock distribution networks<sup>(34)</sup>. A novel 3D Through-Silicon-Via (TSV) based capacitor is investigated in (35) for LC resonant clocking in 3D ICs. Replacing conventional inductor and capacitor to TSV based structures achieves a  $2.2 \times$  and  $16.3 \times$  reduction in area, respectively. A new scheme to use idle TSVs to form inductors in LC resonant clock for 3D ICs to reduce the power consumption in the CDN was proposed in (36). Experimental results on industrial designs show that the power consumption is reduced by up to 47.9% compared to square-wave conventional CDNs. A globally integrated power and clock (GIPAC) distribution network was proposed in<sup>(37)</sup> as a means of eliminating the on-chip global clock distribution network. The power and clock signals are integrated in the GIPAC and then separated in the local power and local clock networks using a low-pass and high-pass filters, respectively. The proposed approach does not eliminate the need for the local clock distribution network. The authors of this paper had proposed the integration of the power and clock distribution networks into one network called the Integrated Power and Clock Distribution Network (IPCDN)<sup>(38)</sup>. The proposed IPCDN combines the power and clock networks, thus reduces metal requirements at higher levels and decreases routing complexity. This approach is most suitable for 3D integrated ICs since it significantly reduces the routing complexity of the clock and power distribution networks and reduces the demand on the limited on-chip metal resources. The IPCDN distributes a differential resonant sinusoidal power-clock signals are generated using a differential LC P<sub>wr</sub>\_C<sub>lk</sub> driver. These signals are connected to the V<sub>DD</sub> port of sequential and combinational circuits. The low voltage swing of the differential P<sub>wr</sub>\_C<sub>lk</sub> signals leads to substantial decrease in the required driver strength as compared to full-swing resonant CDNs<sup>(39)</sup>. A clock buffer is needed in the IPCDN in order to extract a full-swing clock signal which supplies the clock port in sequential elements.

The IPCDN has a large capacitance, thus reducing the central voltage of the resonant sinusoidal signal flowing in the IPCDN enables significant reduction in power consumption. In this paper, the authors investigate the power savings in the IPCDN achieved by reducing the central offset voltage at which the  $P_{wr}C_{lk}$  signal oscillates. In the proposed scheme the central offset voltage is reduced to  $V_{DD}/2$  as presented in section 2. Simulation results and analysis are discussed in section 3 and the conclusion of the paper is given in section 4.

## 2 Proposed IPCDN with Differential Power-Clock Signals Centered at Half the Supply Voltage

The IPCDN offers several advantages as compared to traditional CDNs. Combining the clock and power networks reduces routing complexity and metal overhead. In addition, the reduced swing of the  $P_{wr}$ \_ $C_{lk}$  signals decrease the required LC driver strength. In this paper, we investigate the feasibility of reducing the power consumption of the IPCDN by decreasing the DC voltage at which the power-clock signals oscillate from  $V_{DD}$  to  $V_{DD}/2$ .

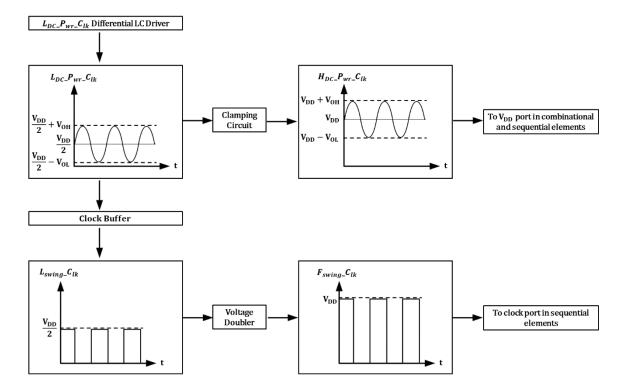

Figure 1 illustrates the IPCDN with power-clock resonant signals centered at high DC voltage, i.e.,  $V_{DD}$ . The generated  $P_{wr}C_{lk}$  signals in this scheme will be referred to as  $H_{DC}P_{wr}C_{lk}$  signals. As shown in Figure 1, the  $H_{DC}P_{wr}C_{lk}$  signals generated by the differential LC driver are connected directly to the  $V_{DD}$  ports of sequential and combinational circuits. The full-swing clock signal,  $F_{swing}C_{lk}$ , extracted by the clock buffer, feeds the clock port in sequential circuits.

Fig 1. IPCDN with  $P_{wr}_{clk}$  signals centered at  $V_{DD}$

The proposed IPCDN with  $P_{wr}C_{lk}$  signals centered at  $V_{DD}/2$  is presented in Figure 2. The differential LC driver generates  $P_{wr}C_{lk}$  signals that are centered at a lower DC voltage, thus refereed to from hereon as  $L_{DC}P_{wr}C_{lk}$ . These signals will be distributed by the IPCDN to reduce the power consumption in this network. The  $L_{DC}P_{wr}C_{lk}$  signals are then fed to a clamping circuit in order to restore the DC component back to  $V_{DD}$  and generate the  $H_{DC}P_{wr}C_{lk}$  signals needed to supply the power port in combinational and sequential circuits. The clock buffer generates a low-swing clock signal,  $L_{swing}C_{lk}$ , with a peak voltage of  $V_{DD}/2$ . A voltage doubler is used to generate a full-swing clock signal,  $F_{swing}C_{lk}$ , to be connected to the clock port in sequential elements.

The generated  $H_{DC}$ \_P<sub>wr</sub>\_C<sub>*lk*</sub> signal presented in Figures 1 and 2 is given by the following equation:

$$H_{DC_{-}}P_{wr_{-}}C_{lk}(t) = \left(\frac{V_{OH} - V_{OL}}{2}\right)\cos\left(2\pi ft - \frac{\pi}{2}\right) + V_{DD}$$

(1)

**Fig 2.** IPCDN with  $P_{wr}C_{lk}$  signals centered at  $V_{DD}/2$ .

The equation for the  $L_{DC} - P_{wr} - C_{lk}$  signal shown in Figure 2 is given by:

$$L_{DC-}P_{wr_{-}}C_{lk}(t) = \left(\frac{V_{OH} - V_{OL}}{2}\right)\cos\left(2\pi f t - \frac{\pi}{2}\right) + \frac{V_{DD}}{2}$$

(2)

Where  $V_{OH}$  and  $V_{OL}$  are the highest and lowest voltage levels of the generated  $P_{wr} C_{lk}$  signal and f is the resonant frequency. The power dissipation of the IPCDN with a  $P_{wr} C_{lk}$  signal centered at  $V_{DD}$  is given by <sup>(16,40,41)</sup>:

$$P_{IPCDN_{-}V_{DD}} = \frac{\pi}{Q} C f V_{DD}^{2}$$

(3)

Where Q is the quality factor of the system, C is the capacitance of the IPCDN and f is the operating frequency.

Similarly, the power dissipation of the IPCDN with a  $P_{wr}$ \_C<sub>lk</sub> signal centered at  $V_{DD}/2$  is given by:

$$P_{IPCDN_{-}}\frac{V_{DD}}{2} = \frac{\pi}{4Q}CfV_{DD}2\tag{4}$$

https://www.indjst.org/

Equations 3 and 4 demonstrate that the power consumption of the IPCDN is proportional to the square of the voltage at which the  $P_{wr}_{lk}$  resonant signal is centered. Reducing this voltage to half achieves a 75% reduction in the power consumption of the IPCDN. Given that the capacitance associated with this global network is high, significant savings in the power consumption can be achieved by the proposed approach. Additional area and power overhead are introduced on the other hand by the clamping circuit and the voltage doubler circuit required to generate the  $H_{DC}_Pw_r_C_{lk}$  and  $F_{swing}_C_{lk}$  signals, respectively.

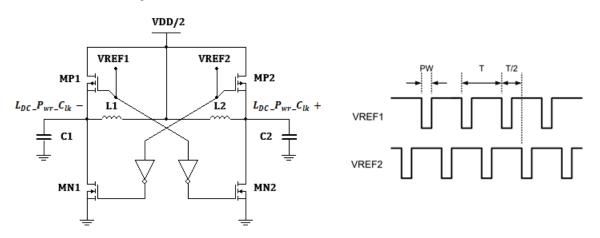

#### 2.1 Differential Pwr\_Clk Driver with Reduced Central Voltage

The LC differential  $P_{wr}C_{lk}$  driver used in the proposed scheme is shown in Figure 3. The  $V_{DD}/2$  node of the inductors determines the central voltage or the DC component around which the generated  $P_{wr}C_{lk}$  signals, i.e.,  $L_{DC}P_{wr}C_{lk}$ + and  $L_{DC}P_{wr}C_{lk}$ - oscillate. Reference pulses VREF1 and VREF2 feed the transistors MP1 and MP2 in order to pull-up the differential  $P_{wr}C_{lk}$  signals to  $V_{OH}$ . The outputs of the two inverters, alternately turn on transistors MN1 and MN2 to pull-down the differential  $P_{wr}C_{lk}$  signals to  $V_{OL}$ .

Fig 3. The LC differential P<sub>wr</sub>\_C<sub>lk</sub> driver with reduced central voltage

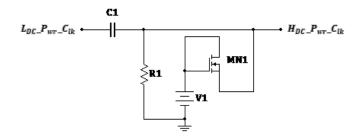

## 2.2 Clamping Circuit

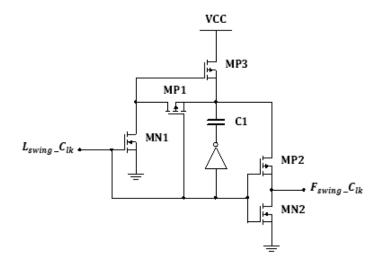

The clamping circuit used in the proposed scheme (Figure 2) is shown in Figure 4. The clamping circuit utilizes a diode connected transistor, MN1, with a suitable DC voltage, V1, and capacitor, C1, to pull up the central voltage of the  $P_{wr}_{Lk}$  differential signals from  $V_{DD}/2$  to  $V_{DD}$ .

Fig 4. The clamping circuit used to pull-up the central DC voltage from  $V_{DD}/2$  to  $V_{DD}$ .

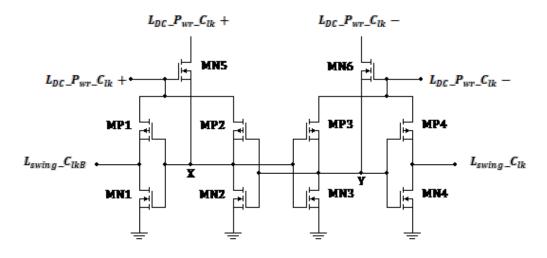

#### 2.3 Clock Buffer

The differential low-swing clock signals,  $L_{swing}$ \_C<sub>*lk*</sub> and  $L_{swing}$ \_C<sub>*lkB*</sub> are extracted from the  $L_{DC}$ \_P<sub>wr</sub>\_C<sub>*lk*</sub> differential signals using the clock buffer presented in Figure 5. The buffer utilizes two cross-coupled CMOS inverters. The first inverter is implemented by MP2 and MN2. The second one is implemented by MP3 and MN3. The gate of each inverter is connected

to the  $L_{DC}P_{wr}C_{lk}$  signals using pass transistors MN5 and MN6. The voltage difference between nodes X and Y shown in the figure is amplified and fed to the two inverters at the output stage implemented by transistors MP1/MN1 and MP4/MN4, respectively, to generate the  $L_{swing}C_{lk}$  and  $L_{swing}C_{lkB}$  signals with sharp edges.

Fig 5. The clock buffer

#### 2.4 Voltage Doubler

The voltage doubler proposed in <sup>(42,43)</sup> and shown in Figure 6 is used to generate full-swing differential clock signals,  $F_{swing}\_C_{lk}$  from the low-swing clock signals,  $L_{swing}\_C_{lk}$ . The full-swing clock signals are connected to the clock port in sequential elements.

Fig 6. The voltage doubler

## **3** Simulation Results and Analysis

All circuits discussed in the previous section were implemented using Tanner 0.25  $\mu$ m CMOS technology and simulated with a supply voltage, V<sub>DD</sub> of 2.5 V. The network capacitance, C was chosen to be equal to 8 pF, for which a 1.267  $\mu$ H is needed in order to generate a P<sub>wr</sub>\_C<sub>lk</sub> signal with a resonant frequency of 50 MHz.

#### 3.1 IPCDN with Pwr\_Clk Signals Centered at VDD

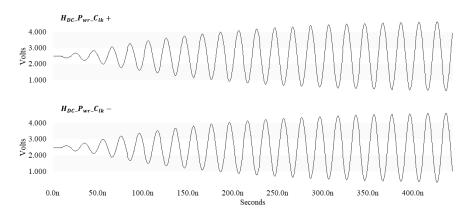

The LC differential  $P_{wr}C_{lk}$  driver with  $V_{DD}$  as the central voltage in the scheme shown in Figure 1 was simulated. In the simulation, the width of the used NMOS devices was 0.3  $\mu$ m and the width of the used PMOS devices was 0.975  $\mu$ m. This sizing of the transistors was selected to ensure that the inverter in the LC differential  $P_{wr}C_{lk}$  driver is a matched inverter. As for the clock buffer, the width of the used PMOS devices and NMOS devices in the simulation was 0.3  $\mu$ m. The differential  $H_{DC}P_{wr}C_{lk}$  signals generated by the LC driver and resonating around a central voltage of 2.5 V are presented in Figure 7. The outputs of the clock buffer, i.e.,  $F_{swing}C_{lk}$  and  $F_{swing}C_{lkB}$  are shown in Figure 8.

**Fig 7.** The differential  $H_{DC}P_{wr}C_{lk}$  signals with 2.5 V as the central voltage

Fig 8. The differential clock signals generated by the clock buffer

#### 3.2 Proposed IPCDN with $P_{wr_{-}}C_{lk}$ Signals Centered at $V_{DD}/2$

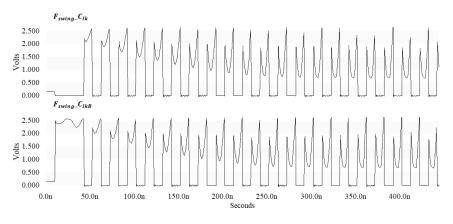

The LC differential  $P_{wr}_{lk}$  driver with  $V_{DD}/2$  as the central voltage in the scheme shown in Figure 3 was simulated. In the simulation, the width of the used NMOS devices was 0.3  $\mu$ m and the width of the used PMOS devices was 2.175  $\mu$ m. This sizing of the transistors was selected to ensure that the inverter in the LC differential  $P_{wr}_{lk}$  driver is a matched inverter. The differential  $L_{DC}_{lk}$  signals generated by the LC driver and resonating around a central voltage of 1.25 V are presented in Figure 9.

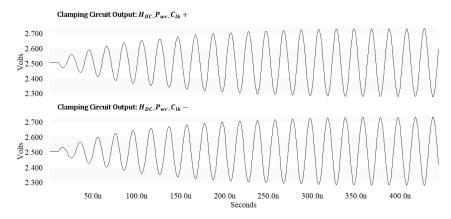

The clamping circuit was simulated using a 100 k $\Omega$  resistance, a 1.2 nF capacitance, and a 3.625 V voltage source. The diode connected transistor (MN1 in Figure 4) has a width of 0.5 um. The H<sub>DC</sub>\_P<sub>wr</sub>\_C<sub>lk</sub> signals generated by the clamping circuit are shown in Figure 9.

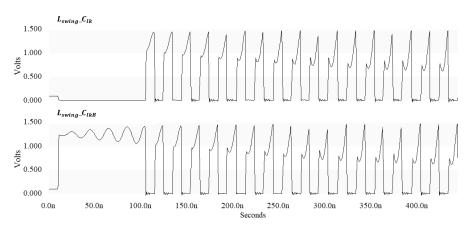

The clock buffer was simulated with NMOS and PMOS devices sized carefully to achieve correct functionality. Figure 11 presents the outputs of the clock buffer, i.e.,  $L_{swing}$ \_C<sub>lk</sub> and  $L_{swing}$ \_C<sub>lkB</sub>.

Fig 9. The differential  $L_{DC}P_{wr}C_{lk}$  signals with 1.25 V as the central voltage

**Fig 10.** The  $H_{DC}_{Pwr}C_{lk}$  signals generated by the clamping circuit

Fig 11. The low-swing differential clock signals generated by the clock buffer

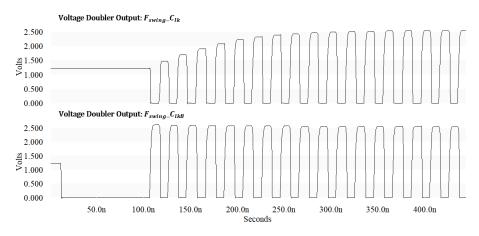

The voltage doubler was simulated using a 1 pF capacitance, and a 1.35 V voltage source. The width of the used NMOS devices is 0.5  $\mu$ m and the width of the used PMOS devices is 0.3  $\mu$ m. The high swing clock signals generated by the voltage doubler are shown in Figure 12.

Fig 12. The full-swing clock signals generated by the voltagedoubler

#### **3.3 Power Consumption Analysis**

The power consumption of the LC differential  $H_{DC}P_{wr}C_{lk}$  driver,  $L_{DC}P_{wr}C_{lk}$  driver, and clock buffer in each scheme are presented in Table 1. Centering the  $P_{wr}C_{lk}$  signals at  $V_{DD}/2$  in the proposed scheme reduces the LC differential  $P_{wr}C_{lk}$  driver power consumption by 75.32% which is consistent with what was previously calculated based on a comparison of equations (3) and (4). Furthermore, the proposed scheme enables a 76.47% reduction in the power of the clock buffer. The clamping circuit and the voltage doubler circuit used by the proposed scheme add additional area and power overhead. The topology of the IPCDN and the number of clamping circuits and voltage doubler circuits needed to drive every section of the IPCDN need to be carefully examined in order to optimize power savings. The area and power overhead introduced by the clamping circuit and the voltage doubler circuit can be reduced by sharing these circuits between several combinational and sequential elements.

| $H_{DC}P_{wr}C_{lk}$ | Power ( $\mu$ W) | $L_{DC}P_{wr}C_{lk}$ | Power ( $\mu$ W) | Reduction in Power |

|----------------------|------------------|----------------------|------------------|--------------------|

| LC driver            | 547              | LC driver            | 135              | 75.32%             |

|                      |                  | + Clamping circuit   | 95               | 57.95%             |

| Clock buffer         | 255              | Clock buffer         | 60               | 76.47%             |

|                      |                  | + Voltage doubler    | 8                | 73.33%             |

#### 3.4 Process, Supply Voltage, and Temperature (PVT) Variation Effects Analysis

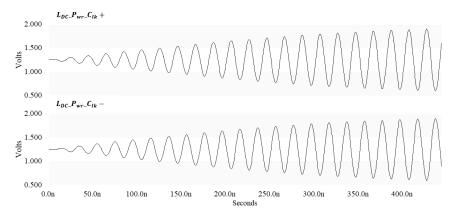

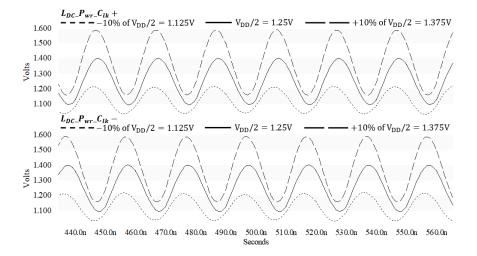

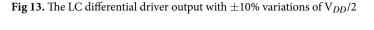

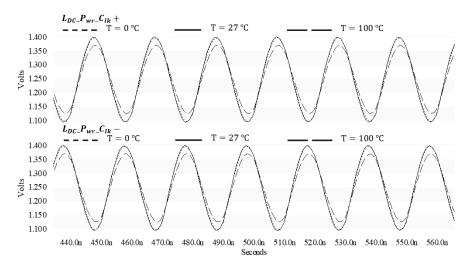

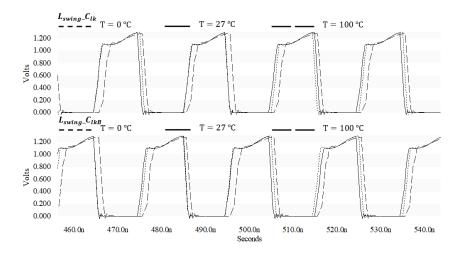

This section discusses the effects of process, supply voltage, and temperature variations (PVT) on the proposed scheme. Simulations were conducted for all of the circuits in the proposed scheme, i.e., the LC differential  $P_{wr}_{L_{lk}}$  driver, the clamping circuit, the clock buffer, and the voltage doubler using minimum sized transistors. The supply voltage was varied by ±10% of  $V_{DD}/2^{(44)}$ . Figures 13 and 14 present the outputs of the LC clock driver and the clock buffer, i.e., the  $L_{DC}_{wr}_{C_{lk}}$  and  $L_{swing}_{L_{lk}}$  signals, respectively under supply voltage variations. The results obtained illustrate that the clock buffer in the proposed scheme is susceptible to drops in the supply voltage. Based on these results, variations in the supply voltage should be carefully considered and tested to ensure correct functionality of IPCDNs.

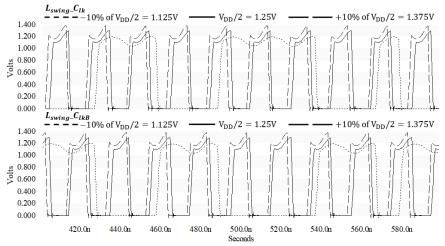

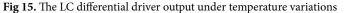

The proposed IPCDN with low central voltage was simulated at  $0 \degree C$ ,  $27 \degree C$ , and  $100 \degree C^{(44)}$ . The simulation results are shown in Figures 15 and 16. The simulation results demonstrate correct functionality of the proposed scheme at low temperature, and at high temperature.

Fig 14. The clock buffer output with  $\pm 10\%$  variations of  $V_{DD}/2$

Fig 16. The clock buffer output under temperature variations

## **4** Conclusion

In this paper, an IPCDN with differential power-clock signals centered at half the supply voltage as a mean to enable power reduction in this network is proposed. All of the components associated with the proposed network including the LC differential power-clock driver, the clock buffer, the clamping circuit, and the voltage doubler circuit were simulated using Tanner 0.25  $\mu$ m technology at a frequency of 50 MHz. Simulation results verify correct functionality of all the components under the proposed scheme. Power reductions of 75.32% and 76.47% were achieved in the LC differential power-clock driver and clock buffer, respectively. The effects of process, voltage supply, and temperature (PVT) variations on the proposed scheme were also investigated. The results show that the components of the proposed scheme are immune to process, supply voltage, and temperature variations, except for the clock buffer which is susceptible to power supply variations. The clamping circuit and the voltage doubler circuit setween several combinational and sequential elements. Future work will concentrate on implementing this scheme at advanced technology nodes with higher frequencies and lower supply voltage. Alternative designs will be explored to reduce circuit complexity and additional overhead of the components used.

#### Acknowledgement

This research was funded by the American University of Kuwait.

## References

- 1) Islam R, Low-Power. Low-Power Resonant Clocking Using Soft Error Robust Energy Recovery Flip-Flops. *Journal of Electronic Testing*. 2018;34(4):471–485. Available from: https://doi.org/10.1007/s10836-018-5737-6.

- 2) Vaisband I, Friedman EG, Ginosar R, Kolodny A. Low Power Clock Network Design. *Journal of Low Power Electronics and Applications*. 2011;1(1):219–246. Available from: https://dx.doi.org/10.3390/jlpea1010219.

- 3) Naffziger SD, Hammond G. The implementation of the next-generation 64 b Itanium/sup TM/ microprocessor. In: and others, editor. 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.02CH37315). IEEE. 2002;p. 344–472. Available from: https://doi. org/10.1109/ISSCC.2002.993073.

- 4) Sathe VS, Arekapudi S, Ishii A, Ouyang C, Papaefthymiou MC, Naffziger S. Resonant-Clock Design for a Power-Efficient, High-Volume x86-64 Microprocessor. IEEE Journal of Solid-State Circuits. 2013;48(1):140–149. Available from: https://dx.doi.org/10.1109/jssc.2012.2218068.

- Chan SC, Restle PJ, Bucelot TJ, Liberty JS, Weitzel S, Keaty JM, et al. A Resonant Global Clock Distribution for the Cell Broadband Engine Processor. IEEE Journal of Solid-State Circuits. 2009;44(1):64–72. Available from: https://dx.doi.org/10.1109/jssc.2008.2007147.

- 6) Talpes E, Marculescu D. Toward a multiple clock/voltage island design style for power-aware processors. *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems. 2005;13(5):591–603. Available from: https://dx.doi.org/10.1109/tvlsi.2005.844305.

- 7) Liang J, Sheikholeslami A, Tamura H, Ogata Y, Yamaguchi H. Loop Gain Adaptation for Optimum Jitter Tolerance in Digital CDRs. IEEE Journal of Solid-State Circuits. 2018;53(9):2696–2708. Available from: https://dx.doi.org/10.1109/jssc.2018.2839038.

- 8) Anderson CJ, Petrovick J, Keaty JM, Warnock J, Nussbaum G, Tendier JM, et al. Physical design of a fourth-generation POWER GHz microprocessor. In: and others, editor. 2001 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. ISSCC (Cat. No.01CH37177). IEEE. 2001;p. 232–233. Available from: https://doi.org/10.1109/ISSCC.2001.912617.

- Pavlidis VF, Savidis I, Friedman EG. Clock Distribution Networks in 3-D Integrated Systems. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2011;19:2256–2266. Available from: https://dx.doi.org/10.1109/tvlsi.2010.2073724.

- 10) Kuttappa R, Taskin B, Lerner S, Pano V, Savidis I. Robust Low Power Clock Synchronization for Multi-Die Systems. In: and others, editor. 2019 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED). IEEE. 2019. Available from: https://doi.org/10.1109/ISLPED.2019.8824957.

- Bezzam I, Mathiazhagan C, Raja T, Krishnan S. An Energy-Recovering Reconfigurable Series Resonant Clocking Scheme for Wide Frequency Operation. IEEE Transactions on Circuits and Systems I: Regular Papers. 2015;62(7):1766–1775. Available from: https://dx.doi.org/10.1109/tcsi.2015.2423797.

- 12) Chan SC, Restle PJ, Bucelot TJ, Liberty JS, Weitzel S, Keaty JM, et al. A Resonant Global Clock Distribution for the Cell Broadband Engine Processor. IEEE Journal of Solid-State Circuits. 2009;44(1):64–72. Available from: https://dx.doi.org/10.1109/jssc.2008.2007147.

- 13) Fuketa H, Nomura M, Takamiya M, Sakurai T. Intermittent Resonant Clocking Enabling Power Reduction at Any Clock Frequency for Near/Sub-Threshold Logic Circuits. *IEEE Journal of Solid-State Circuits*. 2014;49(2):536–544. Available from: https://dx.doi.org/10.1109/jssc.2013.2294172.

- 14) Mahmoodi H, Tirumalashetty V, Cooke M, Roy K. Ultra Low-Power Clocking Scheme Using Energy Recovery and Clock Gating. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2009;17(1):33–44. Available from: https://dx.doi.org/10.1109/tvlsi.2008.2008453.

- 15) Rosenfeld J, Friedman EG. Design Methodology for Global Resonant \${H}\$-Tree Clock Distribution Networks. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*. 2007;15(2):135–148. Available from: https://dx.doi.org/10.1109/tvlsi.2007.893576.

- 16) Sathe VS, Arekapudi S, Ishii A, Ouyang C, Papaefthymiou MC, Naffziger S. Resonant-Clock Design for a Power-Efficient, High-Volume x86-64 Microprocessor. IEEE Journal of Solid-State Circuits. 2013;48(1):140–149. Available from: https://dx.doi.org/10.1109/jssc.2012.2218068.

- Ahn S, Kang M, Kim T. Power-aware inductor analysis in resonant clock networks. 2013 International SoC Design Conference (ISOCC). 2013;p. 5–8. doi:10.1109/ISOCC.2013.6863954.

- Lin PY, Fahmy HA, Islam R, Guthaus MR. LC resonant clock resource minimization using compensation capacitance. 2015 IEEE International Symposium on Circuits and Systems (ISCAS). 2015;p. 1406–1409. doi:10.1109/ISCAS.2015.7168906.

- 19) Liu W, Chen G, Wang Y, Yang H. Modeling and optimization of low power resonant clock mesh. *The 20th Asia and South Pacific Design Automation Conference*. 2015;p. 478–483. doi:10.1109/ASPDAC.2015.7059052.

- 20) Hansson M, Mesgarzadeh B, Alvandpour A. 1.56 GHz On-chip Resonant Clocking in 130nm CMOS. In: and others, editor. IEEE Custom Integrated Circuits Conference 2006. IEEE. 2006;p. 241–244. doi:10.1109/CICC.2006.320947.

- 21) Esmaeili SE, Al-Khalili AJ, Cowan GER. Dual-edge triggered sense amplifier flip-flop for resonant clock distribution networks. IET Computers & Digital Techniques. 2010;4(6):499–514. Available from: https://dx.doi.org/10.1049/iet-cdt.2010.0005.

- 22) Fischer T, Arekapudi S, Busta E, Dietz C, Golden M, Hilker S, et al. Design solutions for the Bulldozer 32nm SOI 2-core processor module in an 8-core CPU. In: and others, editor. 2011 IEEE International Solid-State Circuits Conference. IEEE. 2011;p. 78–80. doi:10.1109/ISSCC.2011.5746227.

- 23) Kurd N, Chowdhury M, Burton E, Thomas TP, Mozak C, Boswell B, et al. Haswell: A Family of IA 22 nm Processors. *IEEE Journal of Solid-State Circuits*. 2015;50(1):49–58. Available from: https://dx.doi.org/10.1109/jssc.2014.2368126.

- 24) Sathe VS, Arekapudi S, Ishii A, Ouyang C, Papaefthymiou MC, Naffziger S. Resonant-Clock Design for a Power-Efficient, High-Volume x86-64 Microprocessor. IEEE Journal of Solid-State Circuits. 2013;48(1):140–149. Available from: https://dx.doi.org/10.1109/jssc.2012.2218068.

- 25) Restle P, Shan D, Hogenmiller D, Kim Y, Drake A, Hibbeler J, et al. 5.3 Wide-frequency-range resonant clock with on-the-fly mode changing for the POWER8<sup>TM</sup> microprocessor. In: and others, editor. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC);vol. 57. IEEE. 2014;p. 100–101. doi:10.1109/ISSCC.2014.6757355.

- 26) Lin BR, Lin GH, Jian A. Resonant Converter with Voltage-Doubler Rectifier or Full-Bridge Rectifier for Wide-Output Voltage and High-Power Applications. *Electronics*. 2018;8(1):3–3. Available from: https://dx.doi.org/10.3390/electronics8010003.

- 27) ur Rahman F, Sathe V. Quasi-Resonant Clocking: Continuous Voltage-Frequency Scalable Resonant Clocking System for Dynamic Voltage-Frequency Scaling Systems. *IEEE Journal of Solid-State Circuits*. 2018;53(3):924–935. Available from: https://dx.doi.org/10.1109/jssc.2017.2780219.

- 28) Ahn S, Kang M, Papaefthymiou MC, Kim T. Synthesis of resonant clock networks supporting dynamic voltage/frequency scaling. In: and others, editor. 20th Asia and SouthPacific Design Automation Conference. 2015;p. 484–489. doi:10.1109/ASPDAC.2015.7059053.

- 29) Yoon CS, Ko HG, Kang BJ, Sull JW, Jeong DK. Deog-Kyoon Jeong, "0.78-mW/pF/GHz, 12.5-GHz Quadrature Resonant Clock with Frequency Tuning Capacitor. 35th International Technical Conference on Circuits/Systems, Computers and Communications. 2020;p. 65–68. Available from: https://ieeexplore.ieee.org/document/9183235.

- 30) Takahashi Y, Sekine T, Yokoyama M. A verification of resonant clock driver design for the IoT era. In: and others, editor. 2017 12th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT). IEEE. 2017;p. 268–270. doi:10.1109/IMPACT.2017.8255895.

- 31) Veadesh B, Ravi S, Venkatapragadeesh B. Design and Analysis of an efficient 3D Network On Chip (NoC) Router. In: and others, editor. 2018 International Conference on Recent Innovations in Electrical, Electronics & Communication Engineering (ICRIEECE). IEEE. 2018;p. 1857–1862. doi:10.1109/ICRIEECE44171.2018.9009362.

- 32) Chentouf M, Cherif L, Ismaili ZEAA. Power-aware clock routing in 7nm designs. In: and others, editor. 2018 4th International Conference on Optimization and Applications (ICOA). IEEE. 2018;p. 1–6. doi:10.1109/ICOA.2018.8370505.

- 33) Tian Y, Watanabe T. Improved delay-matching bus routing by using multi-layers. In: and others, editor. 2015 International Conference on Electronic Packaging and iMAPS All Asia Conference (ICEP-IAAC). IEEE. 2015;p. 708–713. doi:10.1109/ICEP-IAAC.2015.7111103.

- 34) International Technology Roadmap for Semiconductors. Semiconductor Industry Association. 2005. Available from: https://www.semiconductors.org/ resources/2005-international-technology-roadmap-for-semiconductors-itrs/.

- 35) Luo S, Chen B, Li K, Zhuo C, Shi Y. Novel LC resonant clocking for 3D IC using TSV-inductor and capacitor. In: and others, editor. 2017 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS). IEEE. 2017;p. 1–3. doi:10.1109/EDAPS.2017.8277019.

- 36) Tida UR, Zhuo C, Liu L, Shi Y. Dynamic Frequency Scaling Aware Opportunistic Through-Silicon-Via Inductor Utilization in Resonant Clocking. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*. 2020;39(2):281–293. Available from: https://dx.doi.org/10.1109/tcad.2018. 2887053.

- 37) Jakushokas R, Friedman EG. Globally integrated power and clock distribution network. In: and others, editor. Proceedings of 2010 IEEE International Symposium on Circuits and Systems. IEEE. 2010;p. 1751–1754. doi:10.1109/ISCAS.2010.5537570.

- 38) Esmaeili SE, Al-Kahlili AJ. Integrated Power and Clock Distribution Network. IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 2013;21(10):1941–1945. Available from: https://dx.doi.org/10.1109/tvlsi.2012.2219630.

- 39) Esmaeili SE, Al-Khalili AJ, Cowan GER. Estimating required driver strength in the resonant clock generator. In: and others, editor. 2010 IEEE Asia Pacific Conference on Circuits and Systems. IEEE. 2010;p. 927–930. doi:10.1109/APCCAS.2010.5774879.

- 40) Bezzam I, Krishnan S. A pulsed resonance clocking for energy recovery. In: and others, editor. 2014 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE. 2014;p. 2760–2763. doi:10.1109/ISCAS.2014.6865745.

- 41) Bezzam I, Mathiazhagan C, Raja T, Krishnan S. An Energy-Recovering Reconfigurable Series Resonant Clocking Scheme for Wide Frequency Operation. IEEE Transactions on Circuits and Systems I: Regular Papers. 2015;62(7):1766–1775. Available from: https://dx.doi.org/10.1109/tcsi.2015.2423797.

- 42) Verma N, Chandrakasan AP. A 65nm 8T Sub-Vt SRAM Employing Sense-Amplifier Redundancy. In: and others, editor. 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. IEEE. 2007;p. 328–329. doi:10.1109/ISSCC.2007.373427.

- 43) Verma N, Chandrakasan AP. A 256 kb 65 nm 8T Subthreshold SRAM Employing Sense-Amplifier Redundancy. *IEEE Journal of Solid-State Circuits*. 2008;43(1):141–149. Available from: https://dx.doi.org/10.1109/jssc.2007.908005.

- 44) Weste NH, Harris D, Design V. CMOS VLSI Design: A Circuits and Systems Perspective. Noida, India. Pearson Education India. 2015.