# FPGA Implementation of High Speed Digital Pulse Width Modulator (DPWM) Technique for DC-DC Converter

#### K.K. Varsha\* and P.R. Savitha

School of Electronics and Communication, REVA University, Yelahanka, Bangalore – 560064, Karnataka, India; varshakumarswamy@gmail.com, prsavitha@reva.edu.in

#### Abstract

**Objectives:** Digital Pulse Width Modulator (DPWM) remains essential element in power controlling devices that command power switch of power converters. The focus of this study is to structure DPWM of FPGA base for DC chopper. **Methods:** Buck, Boost, Buck and Boost convertor versions are developed in MATLAB-SIMULINK. Verilog coding is performed for Digital Controller to operate for greater rates, which may be incorporated in high speed surroundings; synthesis is completed utilizing Xilinx ISE, along with Behavioral and Period simulation performed with Xilinx Simulator. After affirmation of code it is downloaded on FPGA Spartan 3AN board. The output is confirmed by means of Oscilloscope. **Findings/Application:** The resulting DPWM is a high speed and less power consuming architecture for Buck, Boost, Buck and Boost DC-DC converter. The utilization of Gray counter and One-hot encoder in DPWM has helped in speed improvement and reduced power consumption. The grey encoding method has fewer states in comparison with the sequential encoding method, which makes them quicker. The output is a Pulse-Width Modulation (PWM) signal, for varying clock frequency and duty cycle. The power consumed by DPWM for various frequencies was verified in comparison with the high frequency DPWM. For 6 MHz frequency, the power consumed by DPWM is 0.01486 w and that by a high frequency DPWM is 0.01486 w. The proposed DPWM can operate at a maximum frequency of 140.298 MHz. This DPWM is best suited for Buck, Boost, and Buck and Boost DC-DC converters.

**Keywords:** DC–DC Converter, Field Programmable Gate Arrays (FPGA), Pulse-Width Modulation (PWM), Spartan, MATLAB, SIMULINK

### 1. Introduction

Current research tasks focused on boosting stable state along with the dynamic behaviour of DC-DC converters for high-performance, by signaling different techniques of layout and controlling procedures together with the growing trend to applying digital execution included in analog techniques. Because of accelerated progress in Semi-Conductors and also Micro-processor business, digital controller increased in popularity among Pulse-Width Modulation (PWM) converters and can be shooting more than analog techniques because of accessibility of rapid pace microprocessors, versatility and resistance to noise and ecological variations. Additionally, greater curiosity in Field Programmable Gate Arrays (FPGA) has made it more suitable layout platform for digitally controlled power converters<sup>1</sup>.

# 2. PWM

PWM, a modulation method which controls the pulse width, officially the duration of pulse, depends on signal information of modulator. Nevertheless, the modulation method might be used to encode data that has to be transmitted, and also its own primary usage will be to permit the restraint of the power provided to electric apparatus, notably to inertial loads<sup>2</sup>. The standard significance of voltage provided to the load would be managed by the rotation of switch between load and supply and forth in a speedy rate. The more the switch will be on than the off stages, more complex will be the power provided towards the loading. The switching frequency of PWM should be greater compared to that which will impact the load, and that would be to mention the consequent wave form sensed by the load needs to be smooth as you can. A PWM signal isn't constant. Rather, the signal is still on for a portion of its own period off to the others. Even the duty cycle D, refers to proportion of time scale where the signal is currently around. The duty cycle is anywhere from 0, so the signal is necessarily off, to inch, at which the signal is continually on. A 50% D ends in a great square wave. The major PWM benefit is the power loss from switching devices is extremely less. If switch is not turned on, there is no current practically. As soon as the switch is turned on and power has been moved to the load, then there's hardly any drop of voltage throughout the switching. Reduction of power, the product of voltage and current, is hence in each case is near to 0. Even PWM works nicely for controllers, due to its off/on character, quickly will situate the required duty cycle. It has also been applied in some specific communication methods in which its duty cycle was used to communicate information over a communications channel. Like every sort of energy conversion, PWM

drivers or related loads need to be tested and designed to satisfy particular performance and efficacy standards but given the sophistication of waveforms connected with PWM application, precise measurement isn't a very simple job<sup>3</sup>.

### 3. Proposed Architecture

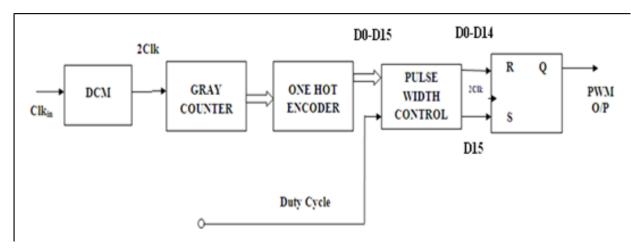

The PWM architecture employed for FPGA is shown in Figure 1 which consists of the following<sup>4</sup>:

- DCM-Itoffers SPARTAN 3A FPGA related applications an enhanced clocking ability<sup>5</sup>. DCM generates a new frequency of clock by multiplying the incoming clock frequency. It also eradicates delay in the external clock input and the clock is reduced. DCM understands the input signal from the CLKIN pin and creates phase changed, clock frequency multiplied (2Clk) values. Here in the design clock doublers (2Clk) is employed.

- *Gray Counter* Grey code assesses the character of binary code or data which consists of on and off indicators, commonly represented by ones and zeros. Grey code is used to check error and clarity correction in binary communications. Grey code is known as reflected binary code. Shifting action is paid off due to one-digit shift in consequence code words.

- One Hot Encoder One hot coding is used to keep away from a comparator, which consumes lot of area and power.

Figure 1. PWM architecture for FPGA.

- *Pulse Width Control* This block is needed, when there is a feedback in the outside circuit, So PWM width automatically corrects depending on the voltage.

- *S-R Flip-Flop* It is used for PWM generation, where inside the Set pin makes the line high and Reset Pins makes it low and thus develops a pulse.

PWM benefit in switching circuits is its low power and higher resolution. The input is compared by binary comparator in traditional PWM architectures together with the counter output signal and resetting the Set-Reset flip-flop alike, thereby producing varying duty cycle. Most important benefit in this architecture will be reduced power consumption and smaller circuit area which would necessitate replacing. Comparator and Binary counter alongside One-hot encoder and Gray counter are used to create variable pulses for DC-DC Converters control. Within this structure, for each positive edge of this clock, Gray counter ends turned on. After attaining a"0000" in the counter output, enable logic is made high, switching on the one-hot encoder behaving like a reset pin to this<sup>6</sup>. One-hot encoder output signal is offered for SR flip -flop pin. PWM controller circuit resets the flip-flop dependent on the duty cycle demand and creates a varying duty cycle. The overall device utilization is listed in Table 1.

| Logic utilization          | Used | Available | Utilization% |  |  |  |  |

|----------------------------|------|-----------|--------------|--|--|--|--|

| Number of Slices           | 23   | 704       | 3%           |  |  |  |  |

| Number of slice flip flops | 32   | 1408      | 2%           |  |  |  |  |

| Number of 4 input LUTs     | 19   | 1408      | 1%           |  |  |  |  |

| Number of bonded IOBs      | 8    | 108       | 7%           |  |  |  |  |

| Number of GCLKs            | 2    | 24        | 8%           |  |  |  |  |

| Number of DCMs             | 1    | 2         | 50%          |  |  |  |  |

## 4. Result

Our project will result in the following:

Table 1. Device utilization summary

- Verilog HDL IP Core for High Throughput DPWM Core.

- A MATLAB-SIMULINK Model for DC-DC convertor for Buck, Boost and Buck-Boost.

- Demonstration of DPWM on FPGA board.

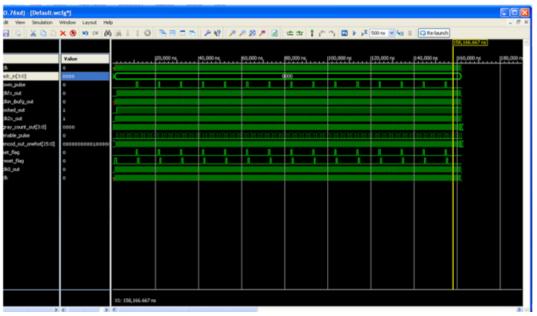

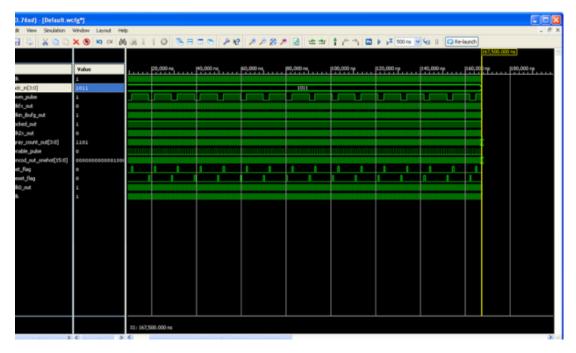

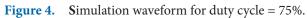

The Xilinx ISE simulation has been used for practical verification of topologies of a PWM generator. Simulations result of 4-bit data entered to PWM device for distinct duty cycle can be seen in Figure 2-4.

**Figure 2.** Simulation waveform for duty cycle = 6%.

| 5xd) - [Defau          |                   |          | u.h.      |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|------------------------|-------------------|----------|-----------|----|------------|-----|------------|------|----------|----|--------|------|---------|------|--------|----------|--------|--------|--------|----------|------------|

|                        | on Window         |          | MRI       | 1. | 0 3        | 8 0 |            | P 12 | 11       | 81 |        | **   | t m     | 10   | , .X   | 500 ns 💌 | 4a II  | C Re-k | aunch  |          | -          |

|                        |                   |          |           |    | 41,720.000 | 116 |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

| Value                  |                   |          | 29,000 ns |    | 1,000 rs   |     | 60,000 rej |      | 80,000 n | 5  | 100,00 | 0.76 | 120,000 | 0.96 | 140,00 | 0.15     | 160,00 | 0.75   | 180,00 | <u>9</u> | 200,000 -4 |

| 1<br>_h(\$ 1000        |                   |          |           |    |            | _   |            |      |          |    |        | .000 |         |      |        |          |        |        |        |          |            |

| 1<br>1<br>1            |                   |          |           | 4  |            |     | Л          | Л    |          |    |        |      |         | U    | μ      | T        | ٣      | J      | Т      |          |            |

| _bu 1                  |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

| M_C 1<br>K_N 1         |                   |          |           |    |            |     |            |      |          |    | -      |      | -       |      |        |          |        |        |        |          | -          |

| _co 0001               |                   | -        |           |    | -          |     |            |      |          |    |        |      | -       |      |        | THE REAL | -      |        | -      |          | -          |

| ble_1 0<br>od_c 100000 |                   |          |           |    | BITTET     |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

| flag 1<br>k_fli 0      | -                 | -        | ĻĻ        |    | _          | -   | 4          | 1    | 1        |    | 1      |      |         |      |        |          |        |        | -      |          | <b></b>    |

| _00E 1                 | ,                 |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          | -          |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

|                        |                   |          |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

| +                      | X1: <b>4</b> 1,72 |          |           |    |            |     |            |      |          |    |        |      |         |      | _      |          |        |        |        |          |            |

| > <                    |                   | 0.000 ms |           |    |            |     |            |      |          |    |        |      |         |      |        |          |        |        |        |          |            |

**Figure 3.** Simulation waveform for duty cycle = 55%.

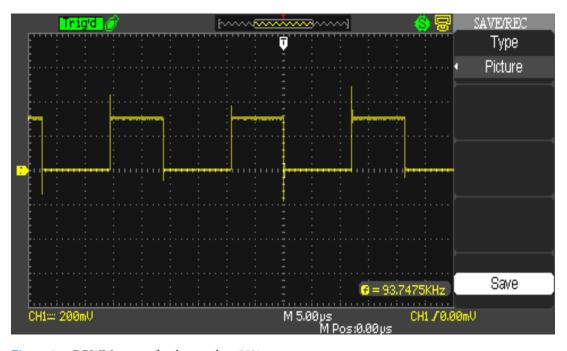

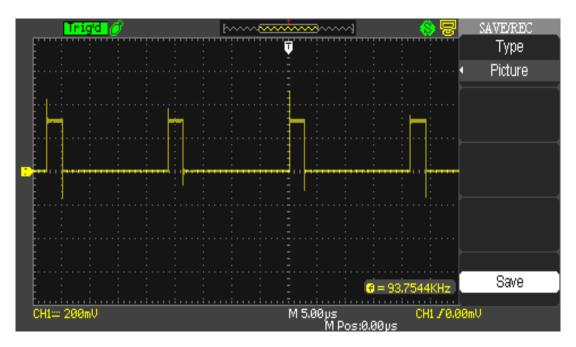

The oscilloscope output Figures 5 and 6 are shown below following the code has been dumped in the FPGA Spartan

3A kit after code verification. The power analysis report for different frequencies can be seen in Table 2.

**Figure 5.** DPWM output for duty cycle = 55%.

**Figure 6.** DPWM output for duty cycle = 6%.

| Darrian                        | Encourses (Mbr) | Power consumption (w) |                     |  |  |  |  |  |  |  |

|--------------------------------|-----------------|-----------------------|---------------------|--|--|--|--|--|--|--|

| Device                         | Frequency (Mhz) | Proposed DPWM         | High frequency DPWM |  |  |  |  |  |  |  |

| SPARTAN 3A                     | 6               | 0.01479               | 0.01486             |  |  |  |  |  |  |  |

| (XC3S50A-4tq144)               | 12.5            | 0.01544               | 0.01549             |  |  |  |  |  |  |  |

|                                | 15              | 0.01569               | 0.01586             |  |  |  |  |  |  |  |

|                                | 25              | 0.01668               | 0.01696             |  |  |  |  |  |  |  |

| SPARTAN 3A<br>(XC3S50A-5tq144) | 6               | 0.01480               | 0.01488             |  |  |  |  |  |  |  |

|                                | 12.5            | 0.01544               | 0.01561             |  |  |  |  |  |  |  |

|                                | 15              | 0.01569               | 0.01561             |  |  |  |  |  |  |  |

|                                | 25              | 0.01569               | 0.01702             |  |  |  |  |  |  |  |

#### Table 2. Power analysis report

#### 5. Conclusion and Future Scope

A new DPWM structure was introduced in this study is to restrain the DC-DC converter. The procedure suggested is based on the grey encoding method; it has fewer states in comparison with the sequential encoding method, which makes them quicker. This DPWM isn't hard to look and can readily alter the resolution too. Based on the FPGA device goal and the amount of control bit inputs the structure operating frequency fluctuates. The suggested DPWM could be implemented in appropriate FPGA device by means of obligatory input control bits and frequency of clock, and as per application requirements. The suggested DPWM structure is examined with SPATRAN 3A FPGA. Resulting PWM signals might be employed for its DC-DC converter to manage the output voltage.

#### 6. References

1. Digital PWM of Cascaded Multilevel Voltage Source Inverter using FPGA. Date accessed: 12/04/2013. https://ieeexplore.ieee.org/document/6547567.

- 2. Peddapelli SK. Recent advances in pulse-width modulation techniques and multilevel inverters, World Academy of Science, Engineering and Technology International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering. 2014; 8(3):600–08.

- Nimbalkar NU, Madake RB, Mulla AM, Patil SD. Studies and simulation based implementation of various PWM strategies for voltage source converter, International Research Journal of Engineering and Technology. 2015; 2(9):691–97.

- Huerta SC, Castro A, Garcia O, Cobos JA. FPGA-based digital pulse width modulator with time resolution under 2 NS, IEEE Transactions on Power Electronics. 2008; 23(6):3135–41. https://doi.org/10.1109/TPEL.2008.2005370.

- Radhika V, Baskaran K. FPGA-based high-frequency digital pulse width modulator architecture for DC-DC converters, Circuits and Systems. 2016; 7(4):464–74. https://doi. org/10.4236/cs.2016.74039.

- FPGA Design and Implementation of Digital PWM Technique for DC-DC Converters. Date accessed: 20/05/2016.https://ieeexplore.ieee.org/document/7807962.