ISSN (Print): 0974-6846 ISSN (Online): 0974-5645

# Design of Low Power 6T-SRAM Cell and Analysis for High Speed Application

#### G. Shivaprakash<sup>1\*</sup> and D. S. Suresh<sup>2</sup>

<sup>1</sup>Department of Electronics and Instrumentation Engineering, M. S. Ramaiah Institute of Technology, Vidya Soudha, MSR Nagar, MSRIT Post, Bangalore, Karnataka, 560054, India; shivaprakash@msrit.edu

<sup>2</sup>Department of Electronics and Communication Engineering, Channabasaveshwara Institute of Technology, N.H. 206, B.H. Road, Gubbi, Tumkur –572216 (Near Bangalore), Karnataka, India; sureshtumkur@yahoo.co.in

#### **Abstract**

Static Random Access Memory (SRAM) is one of the core components in the digital world. Generally, it consumes enormous amount of power and die area. Thereby extensive research in SRAM is in progress related power dissipation, memory chip area and supply voltage requirement. In this paper SRAM analysis in terms of Static Noise Margin, Data Retention Voltage, Read Margin (RM) and Write Margin (WM) for low power application is considered. Static Noise Margin (SNM) is one of the most essential parameter for memory design because it affects both read and write margin. SNM is related to the threshold voltages of the Negative Metal Oxide Semiconductor (NMOS) and Positive Metal-Oxide Semiconductor (PMOS) devices of the SRAM cell. High Read and Write Noise Margin are also significant challenges in the design of SRAM. Data Retention Voltage (DRV) is calculated for 6T-SRAM cell for high-speed application. Different types of curve are taken straightforwardly to analyses the 6t-SRAM by varying the size of the transistor. Performance analysis is estimated in 6T-SRAM designed and implemented in 90nm technology.

Keywords: Data Retention Voltage, Noise Margin, Read Margin, SRAM, 6T-SRAM, Virtuoso, Write Margin

#### 1. Introduction

Nowadays one of the widely used electronic device or electronic circuit is SRAM¹. Stability in SRAM when designed using the Complementary Metal–Oxide–Semiconductor (CMOS) technologies generally depend on the SNM. SRAM memory technology is used because of its speed and robustness. As the device is scaled down in sizes several design challenges arise in the nanometer size SRAM design. In an SRAM cell operation generally supply voltage scaling is performed. The minimum voltage also referred as DRV is the needed for a SRAM

cell to store the data. Reducing the VDD reduces subthreshold leakage current and gate leakage. Conversely, when VDD is reduced too far data loss occurs in SRAM. The DRV is applied to preserve data in the bit cells of SRAM. For analyzing high speed SRAM calculation of read margin and WM is necessary. A significant vision in this paper is to analyze 6T SRAM cell is based on noise marginal by evaluating the DRV, Read Margin and Write Margin. Nowadays focus is on low supply voltage which reduces the SNM. The stability of SRAM cell can be analyzed based on the SNM value because performance is proportional to the SNM. Therefore as SNM reduces

<sup>\*</sup>Author for correspondence

the performance of SRAM cell also reduces or vice versa. For improving the performance of a 6T SRAM cell parameter such as Cell Ratio (CR), Pull up Ratio (PR), Voltage Supplies (VDD) is generally considered. The basic introduction to 6T SRAM cell architecture is provided in section 2, section 3 explains the SRAM working and section 4 to 7 elaborates the SRAM w.r.t SNM, RM, WM and DRV. In the section 8 SRAM Implementation Methodology is provided and SRAM's Simulation Results are explained in detail in section 9. The section is concluded in section 10 and references are provided.

# 2. Static Random Access Memory (SRAM)

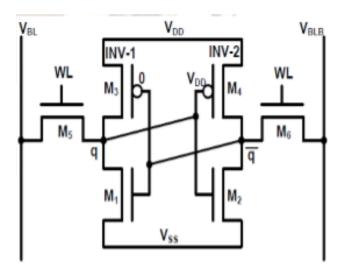

Much digital architecture consists of SRAM. In digital architectures, the density of the design and speed of execution is the most criticized element. Devices are scaled to achieve less complexity, supply voltages and threshold voltages. The Figure 1 represents a 6-Transistor memory cell which is widely accepted as the standard memory cell. To achieve high density, the memory cells should be sized properly a conventional 6T SRAM configuration is considered. This 6T SRAM works on 1V power supply conventional 90 nm for its operation when compared to 1.8V in conventional 180 nm. If the supply voltage applied to the operation of SRAM is low, then power consumption is also scaled down. Data bits to be stored in SRAM are applied to the cross coupled inverters.

**Figure 1.** SRAM Schematic.

These cross coupled inverters have two stable states '0' and '1'. Apart from the cross coupled inverters in SRAM additionally two transistors are connected named access transistors and driver transistor. These two transistors are to control the read operation and write operations of 6T SRAM. The SRAM cell is generally enabled by the Word Line (WL) controlling M5 and M6. The transistors M5 and M6 control data transferring in read and write operations. To improve noise margins two bit lines are typically provided in SRAM. To measure the level of weakness in 6T SRAM, the theory of SNM is applied<sup>2</sup>.

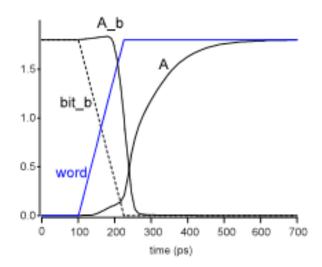

# 3. SRAM Working

The SRAM generally works in three modes of operation, namely hold mode, read mode and write mode<sup>3</sup>. When SRAM is in standby mode or Hold mode the Word Line is connected to ground. SRAM retains the data without flipping the data. Data is retained in the SRAM till power is applied. When the SRAM is in Read mode, bit-line is precharged to VDD and the word-line is set. To read a '0' or '1' the bit-line is generally discharged through the access transistor. Discharging Current is equated through M1 and M5 and is specified in equation 1<sup>4</sup>. The cell ratio is defined as the ratio of the drive transistor and the load transistor. The SNM depend on the Cell Ratio. Therefore it is verified that as the CR increases SNM of the memory cell increases resulting in increase of current in a memory cell [4].

$$\beta_{n,Ms} \left\{ \! \left( \! V_{DD} - V_{QB} - V_{tn} \right) \! V_{DSATn} - \frac{V_{SATn}^2}{2} \! \right\} = \beta_{n,Ms} \left\{ \! \left( \! V_{DD} - V_{tn} \right) \! V_{QB} - \frac{V_{QB}^2}{2} \! \right\} \qquad \left( 1 \right)$$

The equation 1 is simplified to equation 2

$$V_{QB} = \left\{ V_{SSATn} + CR(V_{DD} - V_{tn}) - \sqrt{V_{DSATn}^2 (1 + CR) + CR^2 (V_{DD} - V_{tn})^2} \right\} \div CR \quad (2)$$

Where CR is called the CR or  $\beta$  ratio and is represented in equation 3.

Cell Ratio (CR) =

$$\frac{W_1/L_1}{W_5/L_5}$$

(3)

If the SRAM is working write mode, the bit-lines in the SRAM are always complementary and to store '0' or '1' discharging through the access transistor is necessary<sup>5</sup>. The PR is defined as the ratio of the load transistor and the access transistor. Therefore it is verified that as the PR increases SNM of the memory cell increases. Current passing through M4 and M6 are equated in equation 4<sup>6</sup> to ensure that write is success<sup>7</sup>.

$$\beta_{n,mn6} \left\{ (V_{DD} - V_{tn})V_Q - \frac{V_Q^2}{2} \right\} = \beta_{p,M4} \left\{ (V_{DD} - V_{tp})V_{DSATp} - \frac{V_{DSATp}^2}{2} \right\}$$

(4)

This equation 4 is simplified to equation 5 as

$$V_{Q} = V_{DD} - V_{tn} - \sqrt{(V_{DD} - V_{tp})^{2} 2 \frac{\mu_{p}}{\mu_{n}} PR \left\{ (V_{DD} - V_{tp}) V_{dsatp} - \frac{V_{DSATp}^{2}}{2} \right\}}$$

(5)

Where PR or a Ratio and is represented in equation 6 is

Pullup Ratio (PR) =

$$\frac{W_{4}/L_{4}}{W_{6}/L_{6}}$$

(6)

#### 4. Static Noise Margin

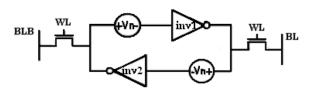

SNM is the square formed in the mutual normal Voltage Transfer Characteristics (VTC) and mirrored voltage transfer characteristics. The values of CR2, PR11 and  $V_{\rm DD}^{-10}$  typically play important roles in the analysis of the SNM of a 6T SRAM cell. SNM should be of High value for high stability of the SRAM cell. Figure 2 represents a general connection for a SRAM bit-cell holding data and to represent SNM.

**Figure 2.** The general setup of SRAM for SNM<sup>2</sup>.

In the SRAM cell SNM is also dependent on RM and write margin. To measure the SNM Butterfly method in 6T SRAM cell is mostly considered where the voltage transfer characteristics curves are rotated to generate butterfly structure<sup>12</sup>.

To calculate SNM in CMOS the drain current is considered and is specified as

$$I_D = \frac{1}{2}\beta (V_{GS} - V_T)^2 \tag{7}$$

$$I_D = \beta V_{DS} \left( V_{GS} - V_T - \frac{1}{2} V_{DS} \right) \tag{8}$$

In the saturated and linear regions, SNM is calculated as

$$SNM_{6T} = V_T - \left(\frac{1}{(k+1)}\right) \left\{ \frac{V_{DD} - \frac{2r+1}{r+1}V_T}{1 + \frac{r}{k(r+1)}} \frac{V_{DD} - 2V_T}{1 + k\frac{r}{q} + \sqrt{\frac{r}{q}} \left(1 + 2k + \frac{r}{q}k^2\right)} \right\}$$

(9)

$$r = ratio = \frac{\beta_d}{\beta_a} \tag{10}$$

$$q = \frac{\beta_p}{\beta_a} \tag{11}$$

$V_{T}$  = Threshold voltage

$$k = \left(\frac{r}{r+1}\right) \left\{ \left\{ \frac{r+1}{r+1 - (V_S)^2 / (V_T)^2} - 1 \right\} \right\}$$

(12)

$$V_{\mathcal{S}} = V_{DD} - V_{T} \tag{13}$$

$$V_r = V_S - \left(\frac{r}{r+1}\right) V_T \tag{14}$$

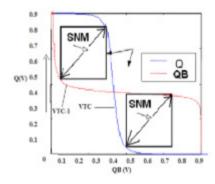

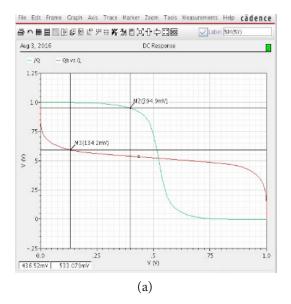

From the graphical analysis the VTC of Inverter 2 (inv2) and inverse VTC 1 from Inverter 1 (inv1) is plotted. The two lobed curves formed are generally referred as "butterfly curve" and are considered for the analysis of the SNM in a SRAM.

Figure 3. Calculation of SNM.

By referring the Figure 3 the SNM can be considered as the side of the two squares formed between the two VTCs of a SRAM cell the VTC of one cell inverter superposes the voltage transfer characteristic (VTC) of the other cell inverter<sup>13</sup>. The two-lobed graph formed is usually known as a "butterfly" curve and is analyzed to determine the SNM of the SRAM. The SNM from this method with respect to curve represented is defined as the side length of the largest square which can be fitted inside the lobes of the "butterfly" curve.

# 5. Read Noise Margin

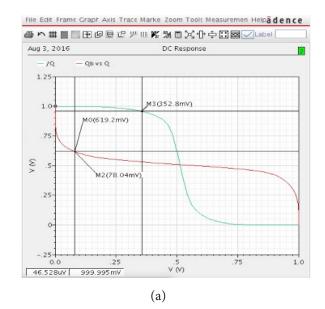

The cell in a read operation it must retain its state. During read operation the cell is vulnerable if the Read-SNM decreases. The reason for vulnerability is that when Read-SNM is calculated the word-line and both the bit-line are pre-charged high. Due to the voltage dividing effect across the access transistor and

drive transits or internal node of the bit-cell representing a zero gets pulled upward through the access transistor thus degrading in SNM during the read operation occurs. The cell may change its state during a read cycle which results in a wrong data. Figure 4 shows VTC curve for RSNM characteristics and based on this curve RM is calculated. The RM defines the read stability of the SRAM cell. In the SRAM cell the data retention in standby mode and read access is a vital constraint. The SRAM cell stability reduces with supply voltage reduction thereby increasing the leakage current resulting from scaling in the technology. If the value of SNM is increased, the read stability of the SRAM cell increases. Therefore a SRAM cell with high RSNM has good read stability.

**Figure 4.** RM from SNM.

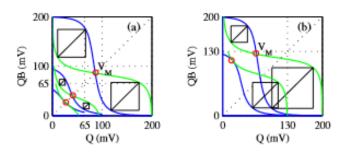

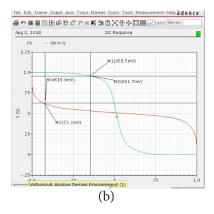

# 6. Write Noise Margin

The write noise margins are obtained by sweeping the inverters (QB and Q). WM is the measure of the ability to write data into the SRAM cell and is defined as the minimum bit-line voltage applied for flipping the state of the SRAM cell. The SRAM Cell write noise margin value usually depends on the cell design and is measured using butterfly curve shown in Figure 5. The input data are sent to the bit-lines during a write mode and to access the cell the word lines are set. If the bit-line is charged to '0' the node of the cell flips state from '1' to '0'. The circuit representing '1' at its output and its bit-line connected to GND is applied to write '0' to that node. WM voltage is considered as the maximum noise voltage at bit lines when write operation is successful. When noise voltages exceeds the WM voltage, then write failure occurs. The most common static approach uses SNM as a criterion. A cell with lower WSNM has poorer write ability.

**Figure 5.** WM Calculation from SNM.

# 7. Data Retention Voltage (DRV)

DVR is the minimum  $V_{\rm DD}$  required for retaining the cell data in the SRAM Cell<sup>15</sup>. In the SRAM cell two nodes (q and  $q_{\rm b}$ ) are available to store values of '0' or '1'<sup>14</sup>. When decreasing the  $V_{\rm DD}$  the data in the SRAM cell remain constant and at a particular voltage there is a flip in the state of SRAM cell, the voltage at which flipping occurs the DVR is obtained.

The Voltage Transfer Curves of the internal inverters degrade to such a level that SNM of the SRAM cell reduces to zero as shown in the Figure 6. If the output of the SRAM cell q='1', q<sub>b</sub>='0', it flips the value toq='0', q<sub>b</sub>='1'. The value of the power supply voltage  $V_{\rm DD}$  decreasing so DVR should be slightly more than the threshold voltage. The threshold voltage is 200mV so below this value in standby/read mode can cause SRAM to flip state.

**Figure 6.** VTC of SRAM cell during DRV calculation.

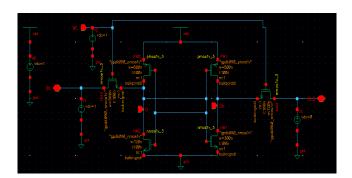

# 8. Implementation Methodology

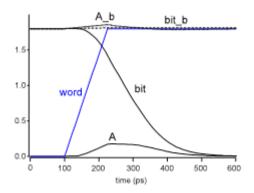

A 6T SRAM is implemented in cadence analog suite in 90nm technology and is represented in Figure 7. Generally in the design the size of NMOS and PMOS transistors is 100nm. To find the CR transistor NM2 is considered as driver transistor and NM3 is considered as the load transistor. The ratio of driver transistor to load transistor considered is in the range of 1 to 2.5 for read operation. Thereby the RM is directly proportional to the cell ratio. To find the PR transistor PM1 is considered as load transistor and NM4 is considered as the access transistor. The ratio of load transistor to access transistor considered is in the range of 3 to 4. Thereby the WM is directly proportional to the PR. The SNM is directly proportional threshold voltage  $V_{Th}$  and the DRV is directly proportional threshold voltage  $V_{Th}$ . For 90nm technology the threshold voltage of 200mV is generally considered.

Figure 7. Schematic diagram of SRAM cell.

#### 9. Simulation Results

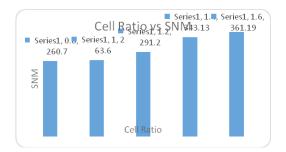

The dependency of SNM with respect to the CR is tabulated in Table 1 and the SNM for CR from 0.8 to 1.6 is plotted in Figure 8 (a) to 8 (e).

Table 1. CR vs SNM

| Cell<br>Ratio | W <sub>1</sub> | $W_{5}$ | $\mathbf{W}_{_3}$ | SNM                |

|---------------|----------------|---------|-------------------|--------------------|

| 0.8           | 1.6 µm         | 2.0 μm  | 6.4 μm            | 394.9-134.2=260.7  |

| 1.0           | 2.0 μm         | 2.0 μm  | 8.0 µm            | 326.3 -62.7=263.6  |

| 1.2           | 2.4 μm         | 2.0 μm  | 9.6 μm            | 352.3-61.1=291.2   |

| 1.4           | 2.8 μm         | 2.0 μm  | 11.2 μm           | 402.4-59.27=343.13 |

| 1.6           | 3.4 μm         | 2.0 μm  | 12.8 μm           | 410.8-49.61=361.19 |

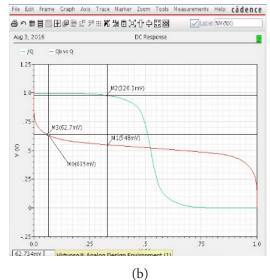

**Figure 8.** (a) SNM vs CR when CR=0.8(b) SNM vs CR when CR=1.0 (c) SNM vs CR when CR=1.2 (d) SNM vs CR when CR=1.4 (e) SNM vs CR when CR=1.6.

As the CR is increased the SNM also increase. But the trade-off is the size of the transistors. For example to get SNM as 263.7mV the CR is just 0.8, it means that it requires less area. Whereas when the SNM is 361.19mV the required CR is 1.6 which is twice the area for 263.7mV SNM. Hence it is inferred from Figure 9 that to get better SNM, areas has to be sacrificed.

Figure 9. Graph of SNM vs CR.

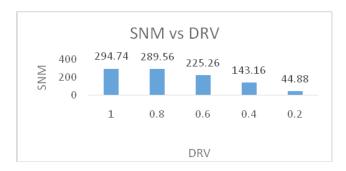

The dependency of SNM with respect to the DRV is tabulated in Table 2 and the SNM for DRV from 1.0 to 0.2 is plotted in Figure 10 (a) to 10 (e).

Table 2. DRV vs SNM

| DRV | SNM                |

|-----|--------------------|

| 1.0 | 362.5-67.76=294.74 |

| 0.8 | 337.0-47.44=289.56 |

| 0.6 | 238.8-13.54=225.26 |

| 0.4 | 159.9-16.74=143.16 |

| 0.2 | 85.03-40.15=44.88  |

**Figure 10.** (a) SNM vs DRV when DRV=0.2(b) SNM vs DRV when DRV=0.4 (c) SNM vs DRV when DRV=0.6 (d) SNM vs DRV when DRV=0.8 (e) SNM vs DRV when DRV=1.0.

For DRV analysis normal  $V_{\rm DD}$ = 1 V for 90nm. The  $V_{\rm DD}$  is reducing till the data is flipped. The data is flipped almost at 200mV because the  $V_{\rm th}$  of the transistors in 90nm technology is 180mV. DRV can't be less than the  $V_{\rm th}$ . For 90nm technology SRAM DRV = 200mV which should be more than the  $V_{\rm th}$  (180mV) Assuming CR = 1 and setting width of transistor M1 and M5 to be 2.0  $\mu$ m

Figure 11. Graph of SNM vs DRV.

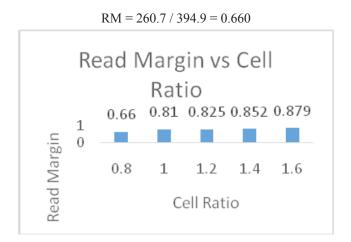

The dependency of SNM with respect to the CR is calculated to find the respective RM which is tabulated in Table 3 and the SNM for CR from 0.8 to 1.6 is plotted in Figure 12 (a) to 12 (e).

Table 3. RM vs SNM

| Cell Ratio | Read Margin | SNM                |

|------------|-------------|--------------------|

| 0.8        | 0.660       | 394.9-134.2=260.7  |

| 1.0        | 0.810       | 326.3 -62.7=263.6  |

| 1.2        | 0.826       | 352.3-61.1=291.2   |

| 1.4        | 0.852       | 402.4-59.27=343.13 |

| 1.6        | 0.879       | 410.8-49.61=361.19 |

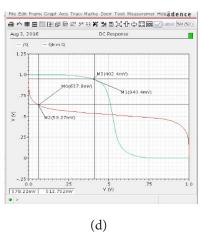

**Figure 12.** (a) RM vs SNM when CR=0.8(b) RM vs SNM when CR=1.0 (c) RM vs SNM when CR=1.2 (d) RM vs SNM when CR=1.4 (e) RM vs SNM when CR=1.6.

The RM is calculated as the ratio of SNM to the maximum value while finding SNM. For example, the RM for the case CR=0.8 is calculated as follows.

Figure 13. Graph of RM vs CR.

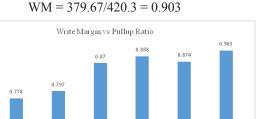

The dependency of SNM with respect to the PR is calculated to find the respective Write Margin which is tabulated in Table 4 and the SNM for PR from 3.0 to 4.0 is plotted in Figure 14 (a) to 14 (f).

Table 4. WM vs SNM

| Pull-up | W4     | W6     | Write  | SNM                |

|---------|--------|--------|--------|--------------------|

| Ratio   |        |        | Margin |                    |

| 3.0     | 360 nm | 120 nm | 0.778  | 352.8-78.04=274.76 |

| 3.2     | 384 nm | 120 nm | 0.797  | 361.7-73.3=288.4   |

| 3.4     | 408 nm | 120 nm | 0.870  | 383.7-49.71=333.99 |

| 3.6     | 432 nm | 120 nm | 0.888  | 389.8-43.36=346.42 |

| 3.8     | 456 nm | 120 nm | 0.874  | 423.7-53.23=370.47 |

| 4.0     | 480 nm | 120 nm | 0.903  | 420.3-40.63=379.67 |

**Figure 14.** (a) WM vs SNM when PR=3.0(b) WM vs SNM when PR=3.2 (c) WM vs SNM when PR=3.4 (d) WM vs SNM when PR=3.6 (e) WM vs SNM when PR=3.8 (f) WM vs SNM when PR=4.0.

As the PR is increased, the SNM is also increased. For example when the PR is 3, the SNM is 274.7mV whereas the SNM is 379.67mV when the PR is 4. It is evident that better SNM can be achieved by sacrificing the area of the transistors. The WM can be calculated as follows

Pullup Ratio

Figure 15. Graph of Write Margin vs Pullup ratio

#### 10. Conclusion

0.92 0.9 0.88 0.86 0.84 0.82 0.8 0.78 0.76

A 6T SRAM is designed using CMOS transistor and implemented in CADENCE design suite in 90nm technology. The SRAM was analyzed by simulating it for parameters like Static Noise Margin. From the SNM, RM and WM are verified and analyzed. The RM and WM are verified by considering the values of CR of 1 to 2.5 and PR of 3 to 4. Performing analysis based on relationship between DRV and SNM, a statistical model is proposed to estimate the DRV value for an SRAM of given size. As the technology is growing, the device dimension is reducing, results in variation of  $V_{\rm TH}$  affecting SRAM cell stability

to great extent. From the simulation results good SNM is obtained by scarifying the area. The DRV of 0.6V is obtained for CR of 1 by setting the width of transistors M1 and M5 same. RM is calculated with respect to SNM is 0.66 and WM with respect to 0.902.

#### 11. References

- 1. Wang CC, Lee PM, Chen KL. An SRAM design using dual threshold voltage transistors and low-power quenchers, IEEE journal of solid-state circuits. 2003 Oct; 38(10):1–8.

- 2. Lohstroh J, Seevinck E, Groot JD. Worst-case SNM criteria for logic circuits and their mathematical equivalence, IEEE journal of Solid-State Circuits.1983 Dec; 18(6):803-7.

- 3. Birla S, Singh RK, Member IACSIT, Pattnaik M. SNM Analysis of various SRAM topologies, IACSIT. International Journal of Engineering and Technology.2011 Jun; 3(3):304–9.

- 4. Keerthi R, Chen H. Stability and SNM analysis of low power SRAM. IEEE International Instrumentation and Measurement Technology Conference, Victoria Canada; 2008 May. p.1541-4.

- 5. K. Anami K, Yoshimoto M, Shinohara H, Hirata Y, Nakano T, Design considerations of a static memory cell, IEEE Journal of Solid-State Circuits. 1983 Aug; 18(4):414-8.

- 6. Wang J, Nalam S, Calhoun BH. Analyzing static and dynamic WM for nanometer SRAMs, Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, VA 22904, USA {jw4pg, svn2u,bcalhoun}@virginia.edu, IEEE Journal of Solid-State Circuits. 2006; 41(1):129-34.

- 7. Calhoun BH, Chandrakasan AP, Analyzing SNM for Subthreshold SRAM in 65nm CMOS, ESSCIRC; 2005.

- 8. Arora G, Poonam, Singh A, SNM Analysis of SRAM Cells at 45nm, 32nm and 22nm technology, International Journal of Engineering Research and General Science. 2014 Jun-Jul; 2(4):785-91.

- 9. Aghababa H, Ebrahimi B, Kusha AA, Pedram M. Probability calculation of read failures in nano-scaled SRAM cells under process variations microelectronics reliability[Internet]. 2012 [Cited 2012 May 25]. Available from:

- 10. Seevinck E, List FJ, Lohstroh J. Static-noise margin analysis of MOS SRAM cells, IEEE Journal of Solid-State Circuits. 1987 Oct; 22:748-54.

- 11. Pavlov A, Sachdev M. CMOS SRAM circuit design and parametric test in nano-scaled technologies. Intel Corporation, University of Waterloo, Springer Science and Business Media B.V; 2008. p.1-202.

- 12. Shin C, Cho MH, Tsukmoto Y, Nguyen BY, Mazure C, Nikolic B, Liu TTK. Performance and area scaling benefits of FD-SOI technology for 6-T SRAM Cells at the 22-nm Node, IEEE Transactions on electron devices. 2010 Jun; 57(6).

- 13. Chandrakasan AP. Low-power CMOS digital design, IEEE Journal of Solid-State Circuits. 1992 Apr; 27:473–84.

- 14. Mukhopadhyay S, Mahmoodi H, Roy K. Statistical design and optimization of SRAM cell for yield enhancement, Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN-47907, USA.

- 15. Pavlov A, Sachdev M. CMOS SRAM circuit design and parametric test in nano-scaled technologies. Intel Corporation, University of Waterloo, 2008 Springer Science and Business Media B.V.; 2008. p.1-202.

- 16. Grossar E. Read stability and write-ability analysis of SRAM Cells for nanometer technologies, IEEE Journal of Solid-State Circuits. 2006 Nov; 41(11):2577–88.

- 17. Ohbayashi S, Yabuuchi M, Nii K, Tsukamoto Y, Imaoka S, Oda Y, Yoshihara T, Igarashi M, Takeuchi M, Kawashima H, Yamaguchi Y, Tsukamoto K, Inuishi M, Makino H, Ishibashi K, Shinohara H. A 65-nm SoC embedded 6T-SRAM designed for manufacturability with read and write operation stabilizing circuits, IEEE Journal of Solid-State Circuits. 2007 Apr; (4):820-9.

- 18. Guo Z, Carlson A, Pang LT, Duong K, Liu TTK, Nikolic B. Large-scale read/WM measurement in 45nm CMOS SRAM arrays, Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720, USA.

- 19. Mazreah AA, Shalmani MTM, Barati H, Barati A, Sarchami A. A low power SRAM base on novel word-line decoding, World Academy of Science, Engineering and Technology. 2008; 39:82-86.